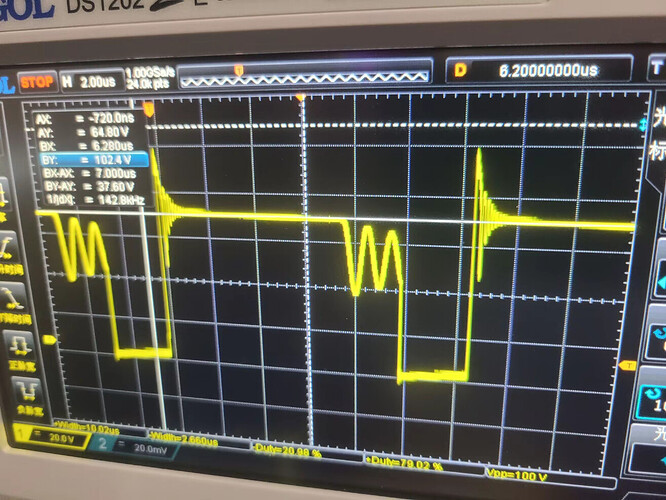

为什么反激电源的Vds波形在DCM模式下后一段的波形会震荡?如下图所示

核心是 “次级箝位消失 + 初级 LC 谐振”,具体逻辑很清晰:

DCM 模式下,当次级电流衰减到零后,次级整流二极管会自动截止 —— 这时候次级没法再通过变压器匝数比,把输出电压反射到初级,相当于 “次级对初级的电压箝位作用消失了”。

而初级侧还残留着漏感(没耦合到次级的电感),加上 MOS 管自身的寄生电容(Coss),这俩会直接构成一个 LC 谐振回路。漏感里没释放完的能量,会在漏感和寄生电容之间反复充放电,进而引发 Vds 波形震荡;又因为 RCD 吸收电路的电阻、MOS 管导通电阻等 “阻尼元件” 会消耗能量,所以震荡幅度会逐渐衰减,直到能量耗完。

简单说就是:次级 “管不住” 初级电压了,初级的漏感和寄生电容就开始 “自由震荡” 了~

DCM模式中次级电流会降到零,当次级电感电流降到了零。这意味着磁芯中的能量已经完全释放了。那么因为二管电流降到了零,二极管也就自动截止了,次级相当于开路状态,输出电压不再反射回初级了。由于此时MOS的Vds电压高于输入电压,所以在电压差的作用下,MOS的结电容和初级电感发生谐振。谐振电流给MOS的结电容放电。Vds电压开始下降,经过1/4之一个谐振周期后又开始上升。由于RCD箝位电路以及其它寄生电阻的存在,这个振荡是个阻尼振荡,幅度越来越小。

这种振荡是断续导通模式(DCM)操作的一个典型特征。它是由变压器的初级励磁电感与MOSFET漏极处的总寄生电容发生谐振所引起的。

波形的这一“后半部分”即所谓的“断续”或死区时间——也就是在副边二极管完成将所有储存能量传递给输出端之后、到初级MOSFET再次导通之前的这段时间。

以下是该现象的逐步解析:

1. 关键元件

振铃现象是由一个典型的LC谐振回路(也称“谐振槽路”)引起的,该回路由以下两个主要元件构成:

- 电感(L): 反激变压器的初级励磁电感(

Lm)。 - 电容(C): 开关节点处的总寄生电容(

C_node)。该电容是多个杂散电容的总和,包括:- MOSFET输出电容(

Coss): 当前处于关断状态的MOSFET漏极与源极之间的电容,通常是主要贡献者。 - 变压器绕组电容(

Cw): 初级绕组匝间存在的电容。 - PCB布局电容: 电路板走线引入的杂散电容。

- MOSFET输出电容(

2. DCM开关周期

为了理解其成因,我们来看DCM开关周期的三个不同阶段:

- MOSFET导通(ON): 开关闭合,初级励磁电感(

Lm)中的电流线性上升,储存能量。此时Vds(漏源电压)接近0V。 - MOSFET关断(能量传递阶段): 开关断开,储存在

Lm中的能量被转移到副边,输出二极管导通。Vds跃升至输入电压(Vin)加上反射输出电压(V_reflected)。 - MOSFET关断(死区时间): 这是关键阶段。在DCM模式下,能量传递在下一个周期开始前就已经完成。

- 副边电流降至零。

- 输出二极管关断。

- 此时,变压器副边相当于从电路中“断开”,而初级侧也处于断开状态(因为MOSFET仍关断)。

- 初级励磁电感(

Lm)此时实际上与总节点电容(C_node)并联。 - 当二极管关断时电压的快速变化会激励这个LC谐振回路,使其以固有的谐振频率开始振荡(即“振铃”):

f_r = 1 / (2\\pi \\sqrt{Lm \\cdot C_{node}}) - 这种(通常为衰减式)振荡将持续,直到MOSFET在下一周期重新导通为止。

3. 这种振铃是否存在问题?

可能有问题,但也可能带来好处:

- 负面影响(EMI): 这种振铃属于高频振荡,可能成为显著的电磁干扰(EMI)源,导致电源无法通过相关法规认证测试。

- 正面影响(谷底开关): 一些智能电源控制器,称为准谐振(QR) 或 谷底开关 控制器,专门设计用于检测这种振铃。它们会刻意在

Vds电压振荡至最低点(即“谷底”)时重新导通MOSFET。这种技术被称为零电压开关(ZVS) 或“软开关”,可显著降低开关损耗,从而大幅提升变换器的整体效率。