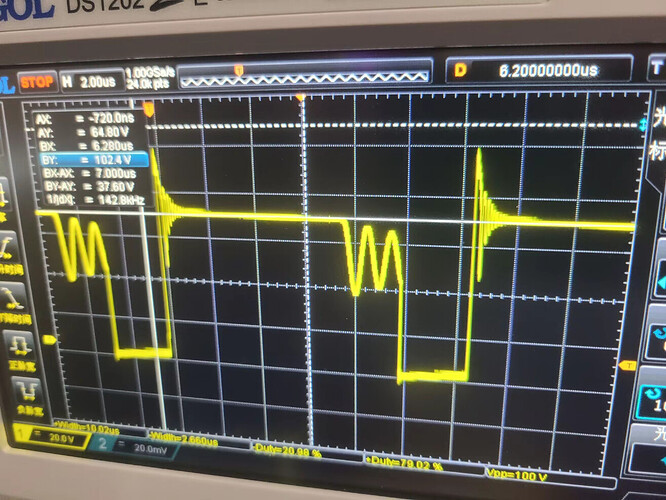

为什么反激电源的Vds波形在DCM模式下后一段的波形会震荡?如下图所示

核心是 “次级箝位消失 + 初级 LC 谐振”,具体逻辑很清晰:

DCM 模式下,当次级电流衰减到零后,次级整流二极管会自动截止 —— 这时候次级没法再通过变压器匝数比,把输出电压反射到初级,相当于 “次级对初级的电压箝位作用消失了”。

而初级侧还残留着漏感(没耦合到次级的电感),加上 MOS 管自身的寄生电容(Coss),这俩会直接构成一个 LC 谐振回路。漏感里没释放完的能量,会在漏感和寄生电容之间反复充放电,进而引发 Vds 波形震荡;又因为 RCD 吸收电路的电阻、MOS 管导通电阻等 “阻尼元件” 会消耗能量,所以震荡幅度会逐渐衰减,直到能量耗完。

简单说就是:次级 “管不住” 初级电压了,初级的漏感和寄生电容就开始 “自由震荡” 了~

DCM模式中次级电流会降到零,当次级电感电流降到了零。这意味着磁芯中的能量已经完全释放了。那么因为二管电流降到了零,二极管也就自动截止了,次级相当于开路状态,输出电压不再反射回初级了。由于此时MOS的Vds电压高于输入电压,所以在电压差的作用下,MOS的结电容和初级电感发生谐振。谐振电流给MOS的结电容放电。Vds电压开始下降,经过1/4之一个谐振周期后又开始上升。由于RCD箝位电路以及其它寄生电阻的存在,这个振荡是个阻尼振荡,幅度越来越小。

這種振盪是 DCM 操作的一個典型特徵。它是由變壓器的初級激磁電感與 MOSFET 漏極處的總寄生電容共振所引起的。

波形的這個「後段」就是所謂的「不連續」或死區時間——也就是在次級二極體已將所有儲存的能量傳遞至輸出端之後,到初級 MOSFET 再次導通之前的這段時間。

以下是此現象的逐步解析:

1. 關鍵元件

這種振鈴現象是由一個典型的LC 諧振槽路(又稱「槽路」)所產生,主要由以下兩個元件組成:

- 電感(L): 返馳式變壓器的初級激磁電感(

Lm)。 - 電容(C): 開關節點處的總寄生電容(

C_node)。此電容是多個雜散電容的總和:- MOSFET 輸出電容(

Coss): 目前關閉狀態的 MOSFET 漏極與源極之間的電容,通常是最大的貢獻者。 - 變壓器繞組電容(

Cw): 初級繞組匝與匝之間的電容。 - PCB 布局電容: 電路板走線所產生的雜散電容。

- MOSFET 輸出電容(

2. DCM 切換週期

為了理解此現象的成因,我們來觀察 DCM 切換週期的三個不同階段:

- MOSFET 導通(ON): 開關關閉,初級激磁電感(

Lm)中的電流上升,儲存能量。此時Vds(汲極-源極電壓)接近 0V。 - MOSFET 關斷(OFF,能量傳遞): 開關打開,

Lm中儲存的能量轉移到次級側,輸出二極體導通。Vds電壓瞬間上升至輸入電壓(Vin)加上反射輸出電壓(V_reflected)。 - MOSFET 關斷(死區時間): 這是關鍵階段。在 DCM 模式下,能量傳遞會在下一個週期開始前就已完成。

- 次級電流降至零。

- 輸出二極體關斷。

- 此時,變壓器次級側等於從電路中「斷開」,初級側也因 MOSFET 關斷而斷開。

- 初級激磁電感(

Lm)現在實際上與節點總電容(C_node)並聯。 - 當二極體關斷時電壓快速變化所產生的「衝擊」激發了這個 LC 槽路,使其以自然諧振頻率開始振盪(振鈴):f_r = 1 / (2\\pi \\sqrt{Lm \\cdot C_{node}})

- 這種(通常會衰減的)振盪會持續,直到下一個週期 MOSFET 再次導通為止。

3. 這種振鈴是問題嗎?

它可能帶來問題,但也可能成為優勢:

- 缺點(EMI): 這種振鈴屬於高頻振盪,可能產生顯著的電磁干擾(EMI),導致電源無法通過法規認證測試。

- 優點(谷底切換): 一些智慧型電源控制器,稱為準諧振(QR)或谷底切換控制器,專門設計用來偵測此振鈴現象。它們會刻意在

Vds電壓振盪至最低點(即「谷底」)時重新導通 MOSFET。這種技術稱為**零電壓切換(ZVS)**或「軟切換」,能大幅降低切換損耗,並提升轉換器的整體效率。