Bài viết này được chuyển ngữ từ tài liệu ứng dụng của TI (ZHCA710 – Jun. 2017)

Tác giả: Wiky Liao / Kevin Zhang

Liên kết tải tài liệu PDF: https://www.123865.com/s/2Y9Djv-1uTdH

Tóm tắt

Cuộn dòng Rogowski PCB với các đặc tính đáp ứng nhanh, độ tuyến tính cao, chi phí thấp, được ứng dụng rộng rãi trong các ứng dụng dòng điện xoay chiều lớn, như điều khiển động cơ xoay chiều, thang cuốn, đường dây trên không và cáp, v.v. Do tín hiệu đầu ra của cuộn Rogowski là đạo hàm của dòng điện gốc, nên cần phải thiết kế mạch tích phân đi kèm. Bài viết này mô tả chi tiết nguyên lý hoạt động và các điểm chính trong thiết kế của cuộn dòng Rogowski PCB, và thiết kế mạch tích phân hiệu năng cao sử dụng khuếch đại thuật toán OPA2333 của TI, có thể giúp khách hàng nhanh chóng thiết kế giải pháp phát hiện dòng điện bằng cuộn dòng Rogowski PCB phù hợp với yêu cầu ứng dụng.

1 RogowskiCuộn dây

1.1 Giới thiệu về cuộn dây Rogowski

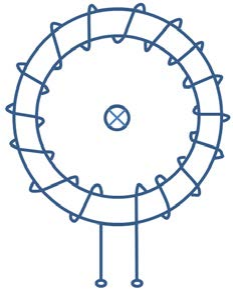

Cuộn dây Rogowski là một cảm biến dòng điện không tiếp xúc, chủ yếu được chia thành hai loại lớn là loại mềm và loại cứng, cuộn dây Rogowski PCB thuộc loại cứng. Đặc điểm cấu trúc của nó là dây dẫn được quấn đều trên khung vòng không từ tính, tạo thành một cuộn dây hình vòng, dòng điện được đo đi qua tâm của cuộn dây, như Hình 1所示.

Hình 1 Hình bên trái là sơ đồ cấu trúc cuộn dây Rogowski, hình bên phải là Layout cuộn dây Rogowski PCB

1.2 Nguyên lý hoạt động của cuộn dây Rogowski

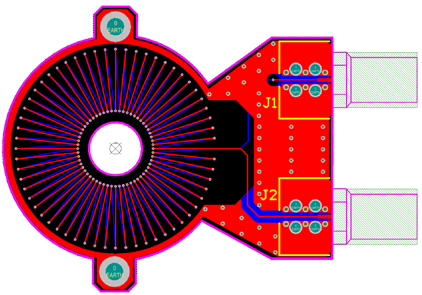

Giả sử một dây dẫn mang dòng điện vô hạn dài đi qua thẳng góc tâm cuộn dây Rogowski, dòng điện trong dây là I. Đường kính trong của cuộn dây là a, đường kính ngoài là b, độ dày của bảng mạch là h, độ từ thẩm của dây dẫn PCB là μ. Như Hình 2所示.

Hình 2 Mô hình phân tích cuộn dây Rogowski, hình bên trái là bản nhìn từ trên xuống, hình bên phải là bản cắt ngang

Theo định luật Biot-Savart, cường độ từ thông tại vị trí x:

Dây dẫn tầng trên và dây dẫn tầng dưới được nối với nhau qua lỗ thông, tạo thành 1 vòng, từ thông sinh ra trên mỗi vòng:

Theo định luật Lenz, điện áp cảm ứng trên cuộn dây N vòng:

Trong công thức (3), M là hệ số tư cảm.

Từ công thức (3) có thể thấy, đầu ra của cuộn dây Rogowski là một điện áp, nó có quan hệ vi phân với dòng điện được đo, do đó cuộn dây Rogowski chỉ phù hợp để đo dòng điện xoay chiều, và khi sử dụng cần phải kết hợp với mạch tích phân.

1.3 Các điểm quan trọng trong thiết kế cuộn dây Rogowski PCB

1.3.1 Giới hạn số vòng

Thông số chính của cuộn dây Rogowski là hệ số tư cảm M, giá trị của nó chủ yếu phụ thuộc vào số vòng, độ dày bảng mạch, đường kính trong và đường kính ngoài của cuộn dây. Trong đó, do bị giới hạn bởi kích thước lỗ thông và mức độ chế tạo PCB, số vòng thực tế không thể vô hạn mà có một giới hạn nhất định. Mô hình tính toán số vòng như Hình 3所示.

Khoảng cách giữa các lỗ thông V1 và V2:

Do giới hạn về mức độ chế tạo, khoảng cách giữa hai lỗ thông liền kề này ít nhất phải lớn hơn 3 lần hiệu số đường kính pad và lỗ thông, tức là:

trong đó V_p là đường kính pad của lỗ thông, V_h là đường kính lỗ thông.

Từ công thức (4) và (5) có thể tính được góc giữa hai lỗ thông liền kề:

Do đó số vòng tối đa của cuộn dây Rogowski PCB:

Nói chung, độ dày bảng mạch cũng quyết định kích thước tối thiểu của lỗ thông, do đó trước khi thiết kế cuộn dây, tốt nhất nên xác nhận với nhà sản xuất PCB.

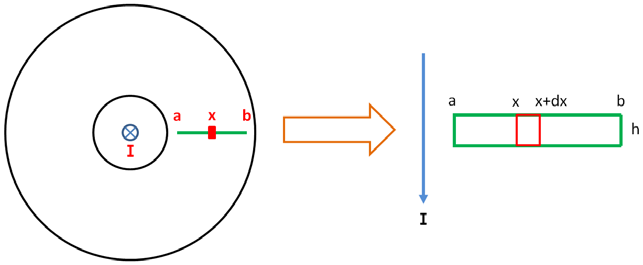

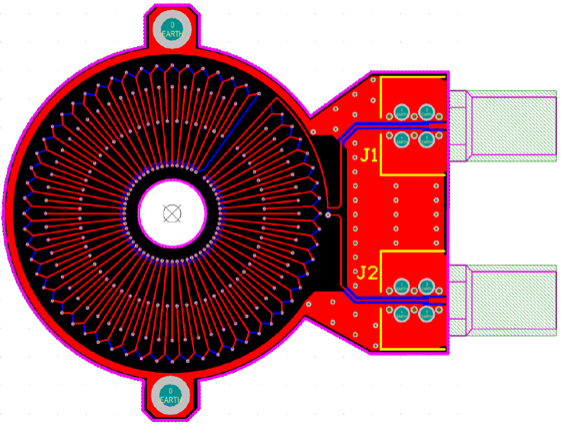

1.3.2 Sử dụng không gian hợp lý

Cuộn dây Rogowski PCB thường được định tuyến theo kiểu phân tán, như vậy sẽ có khoảng trống lớn giữa các vòng dây gần phía ngoài. Do đó có thể thêm các vòng dây nhỏ vào giữa các vòng dây lớn, như vậy trong khi kích thước bảng mạch không đổi, có thể tăng hệ số tư cảm của cuộn dây, như Hình 4所示. Giả sử đường kính trong của vòng dây nhỏ là c, đường kính ngoài là d, thì hệ số tư cảm của cuộn dây:

Hình 4 Cuộn dây Rogowski sau khi thêm vòng dây nhỏ

Trong trường hợp kích thước bảng mạch cố định, nếu cần hệ số tư cảm rất lớn, có thể xem xét việc nối tiếp đầu-cuối nhiều cuộn dây Rogowski PCB, tức là nối đầu ra J2 của Hình 4 với J1 của cuộn dây PCB tiếp theo, để thực hiện cộng dồn tín hiệu.

2 Thiết kế mạch tích phân

2.1 Hạn chế của mạch tích phân lý tưởng và cải tiến

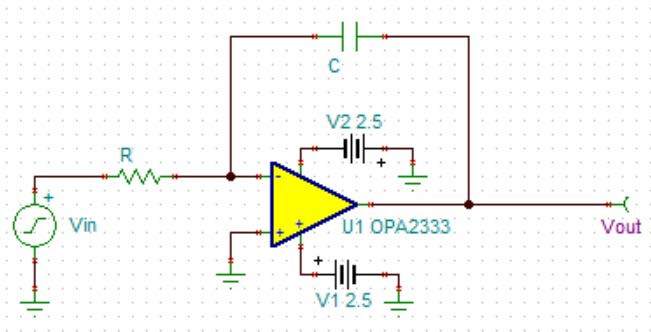

Do điện áp đầu ra của cuộn dây Rogowski là vi phân của tín hiệu dòng điện được đo, nếu không có mạch tích phân ở cấp sau, thì chỉ cần dòng điện có thành phần tần số cao nhẹ cũng sẽ cảm ứng ra điện áp cao ở đầu ra cuộn dây, từ đó làm chìm tín hiệu sóng cơ bản. Do đó cấp sau cần mạch tích phân để khôi phục lại tín hiệu. Mạch tích phân lý tưởng như Hình 5所示.

Hình 5 Hình bên trái là sơ đồ nguyên lý mạch tích phân lý tưởng, hình bên phải là dạng sóng điện áp đầu ra tích phân

Khi lệch của tín hiệu đầu vào bằng không, lệch của tín hiệu sau khi tích phân cũng phải bằng không. Tuy nhiên như hình trên所示, lệch điện áp đầu ra tích phân không bằng không, và dạng sóng đã trôi đến ngưỡng nguồn. Khi op-amp thực tế hoạt động thì tình trạng còn tồi tệ hơn, dạng sóng sẽ bị xén sóng tại ngưỡng nguồn, gây ra méo bão hòa hoặc méo cắt. Nguyên nhân chính là op-amp hiện tại đều không phải là op-amp lý tưởng, nó tồn tại điện áp offset cố hữu. Do không có mạch khác, offset sẽ nạp điện cho tụ tích phân, trong thời gian dài nhất định sẽ dẫn đến bão hòa tụ, gây ra xén sóng. Do đó cần phải mắc song song điện trở hai đầu tụ tích phân, cung cấp mạch xả cho tụ để mạch hoạt động ổn định, như Hình 6所示. Sau khi mắc song song điện trở, cần thiết phải phân tích hiệu năng tích phân của mạch.

Hình 6 Phân tích hiệu năng sau khi mắc song trở cho mạch tích phân

Tại đầu vào nghịch của op-amp, lập phương trình dòng điện Kirchhoff:

Công thức (9) là phương trình bậc nhất không tuyến tính thuần nhất, giải phương trình được:

trong đó C_1 là hằng số. Giả sử tín hiệu đầu vào V_{in} = \cos(\omega t) , thì công thức (10) có thể đơn giản hóa thành:

Từ góc độ miền tần số, hệ số khuếch đại của mạch sau khi mắc song trở:

Công thức (11) và (12) truyền đạt hai thông tin quan trọng:

- Khi thời gian t tăng dần, phần số mũ C_1 e^{-\frac{t}{R_f C}} của điện áp đầu ra V_{out} sẽ dần nhỏ đi, cuối cùng hoàn toàn có thể bỏ qua;

- Khi R_f \gg \frac{1}{\omega C} , \varphi \approx 0^\circ , và hệ số khuếch đại gần với giá trị lý tưởng \frac{1}{\omega RC} , lúc này có thể coi điện áp đầu ra chính là tích phân nghịch đảo của tín hiệu đầu vào.

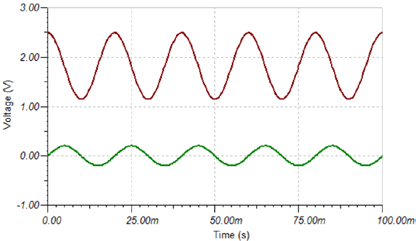

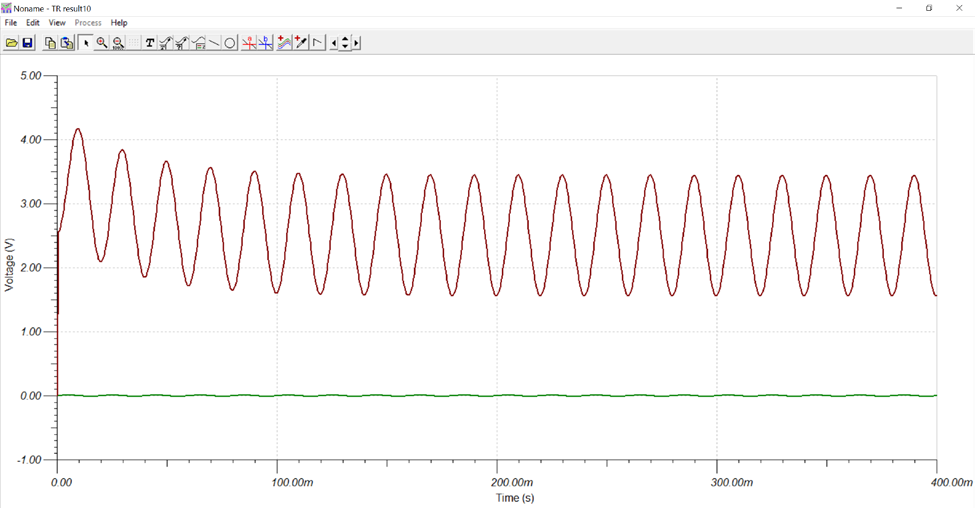

Dựa trên phân tích trên, kết quả mô phỏng mạch tích phân như Hình 7所示. Trong đó đường màu xanh lá là tín hiệu đầu vào, đường màu đỏ là tín hiệu đầu ra. Tín hiệu đầu ra trong giai đoạn đầu bị ảnh hưởng bởi hệ số số mũ nên xuất hiện dao động, nhưng cuối cùng ổn định, hiệu quả tích phân rất tốt.

Hình 7 Dạng sóng mô phỏng mạch tích phân sau khi mắc song trở

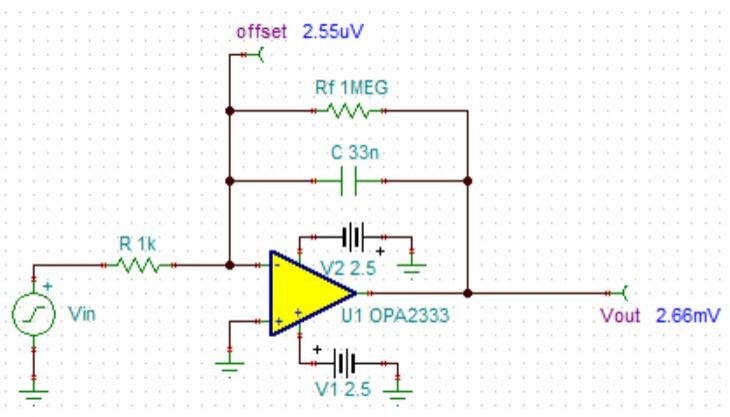

2.2 Lựa chọn op-amp cho mạch tích phân

Để đạt được hiệu quả tích phân tốt, nói chung cần chọn điện trở hồi tiếp Rf càng lớn càng tốt, nhưng không phải càng lớn càng tốt. Nguyên nhân chính là mạch tích phân đối với offset của op-amp mà nói là một mạch khuếch đại đồng pha, điện trở hồi tiếp Rf quá lớn sẽ dẫn đến tồn tại lệch DC lớn ở đầu ra, làm giảm khả năng ức chế trôi tích phân. Do đó op-amp trong mạch tích phân phải có giá trị offset rất nhỏ, để đảm bảo mức DC ở đầu ra càng thấp càng tốt. OPAx333 là một op-amp có offset thấp với chức năng Zero Drift do TI giới thiệu, sử dụng phương pháp hiệu chuẩn số bên trong để giảm đáng kể offset và điện áp trôi, offset tối đa của nó chỉ 10uV, đồng thời có độ trôi thấp đến 0.05uV/°C, rất phù hợp để sử dụng trong thiết kế mạch tích phân. Hình 8 thực hiện mô phỏng DC cho mạch tích phân OPA2333, có thể thấy trong trường hợp điện trở hồi tiếp gấp 1000 lần điện trở tích phân, đầu ra cũng chỉ có 2.66mV, hiệu năng rất tốt. Đồng thời dòng tĩnh tối đa của OPAx333 chỉ 25uA, là một op-amp hiệu năng cao công suất thấp.

Hình 8 Mô phỏng DC mạch tích phân OPA2333

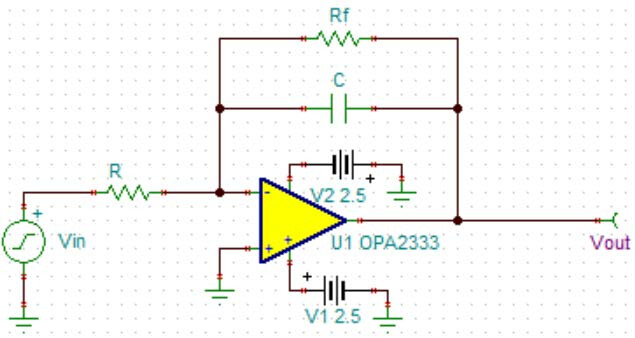

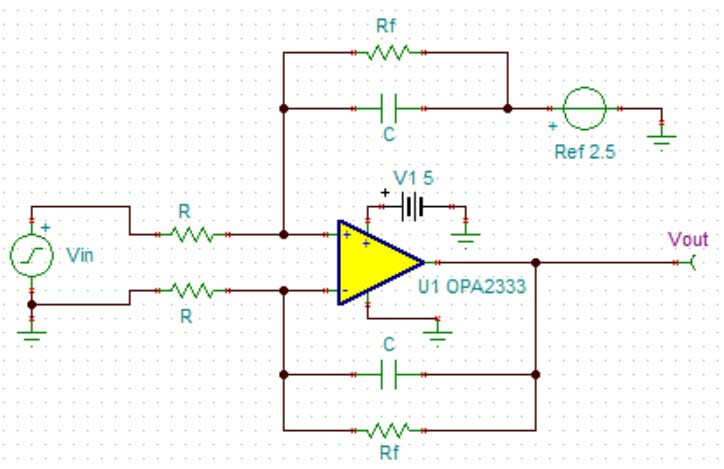

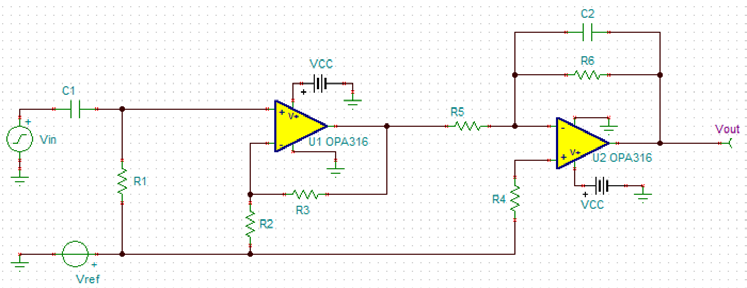

2.3 Thiết kế mạch tích phân nguồn đơn

Các mạch tích phân được đề cập trước đó sử dụng giải pháp tích phân nguồn kép, tuy nhiên nhiều ứng dụng của khách hàng chỉ hỗ trợ cấp nguồn đơn, do đó cần thiết phải thiết kế một loại mạch tích phân nguồn đơn. Tham khảo cấu trúc mạch của op-amp vi sai, thiết kế mạch tích phân nguồn đơn như Hình 9所示.

Hình 9 Mạch tích phân nguồn đơn

Tương tự như phương pháp phân tích trước đó, giả sử điện áp đầu vào V_{in} = \cos(\omega t) , thì điện áp đầu ra:

Giải thích cốt lõi công thức (13):

- Đặc tính đầu ra: Điện áp đầu ra là tích phân đồng pha của tín hiệu đầu vào, đồng thời bao gồm lệch DC V_{ref} ;

- Xác minh mô phỏng: Dạng sóng đầu ra mô phỏng tương ứng với Hình 10, trong đó đường màu xanh lá là tín hiệu đầu vào, đường màu đỏ là tín hiệu đầu ra, hiệu năng tích phân của hệ thống rất tốt.

Hình 10 Dạng sóng mô phỏng mạch tích phân nguồn đơn

2.4 Các lưu ý cho mạch tích phân hiệu năng cao

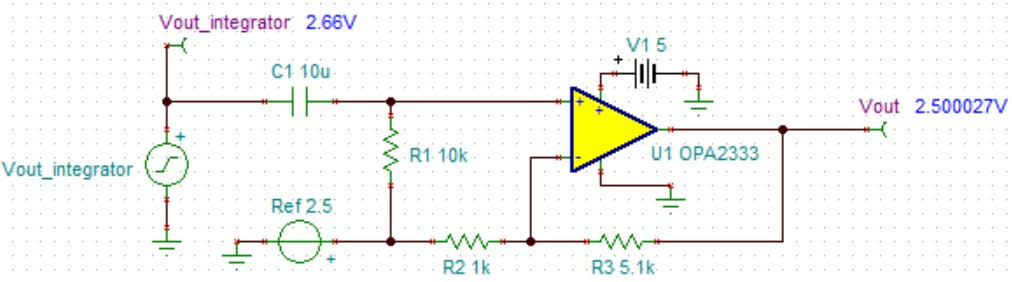

2.4.1 Hiệu chỉnh lệch

Từ phân tích mạch ở trên, ta biết rằng lệch điện áp ở đầu ra có một sai số nhất định, đối với op-amp OPAx333 thì tối đa chỉ có vài mV (đối với op-amp kém hơn có thể đạt đến vài trăm mV). Nếu yêu cầu về lệch ở đầu ra cao, thì cần phải hiệu chỉnh lại lệch, mạch hiệu chỉnh nằm ở cấp sau mạch tích phân, như Hình 11所示. Từ kết quả mô phỏng có thể thấy, lệch DC ở đầu ra Vout chỉ chênh lệch 27uV so với giá trị Ref đã đặt trước, hiệu quả hiệu chỉnh lệch rất tốt. Đồng thời điện trở tỷ lệ đồng pha R2 và R3 có thể điều chỉnh tín hiệu thêm một bước nữa, làm cho đầu ra đạt biên độ đầy đủ.

Hình 11 Mạch hiệu chỉnh lệch và kết quả mô phỏng DC

2.4.2 Đo lường thành phần lỗi tần số cao

Trong một số ứng dụng (như AFCI), người dùng chủ yếu quan tâm đến thành phần lỗi tần số cao của dòng điện, để có thể thực hiện các hành động tương ứng trong trường hợp lỗi (như cắt mạch), lúc này dòng điện làm việc bình thường trong dải tần số thấp không còn quan trọng nữa, thậm chí có thể bỏ qua. Đối với trường hợp ứng dụng này, có thể đặt một bộ lọc thông cao trước tiên, để lọc bỏ thành phần tần số thấp. Sau đó thêm một mạch khuếch đại, làm tăng tín hiệu thành phần tần số cao, đảm bảo tín hiệu sau tích phân đủ lớn để có thể được giám sát, mạch ứng dụng như Hình.12所示.

Hình 12 Mạch đo lường thành phần lỗi tần số cao

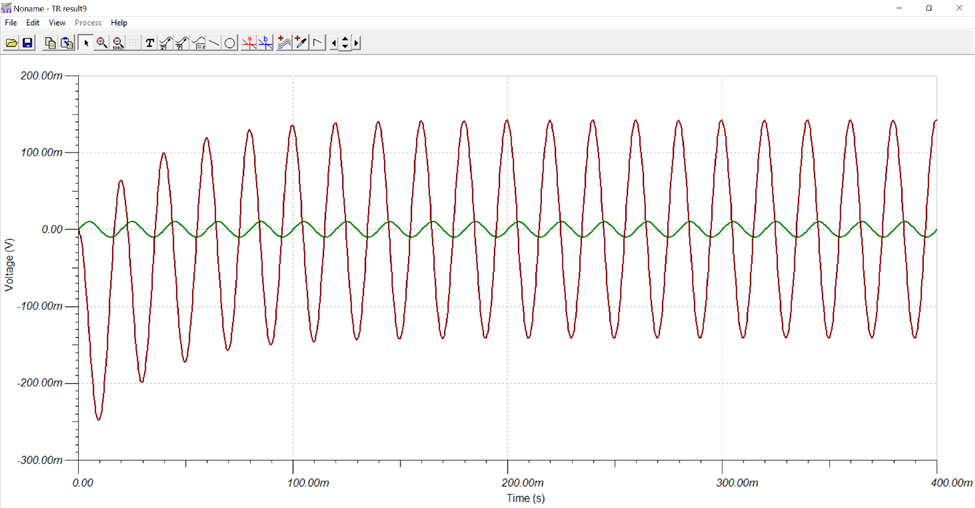

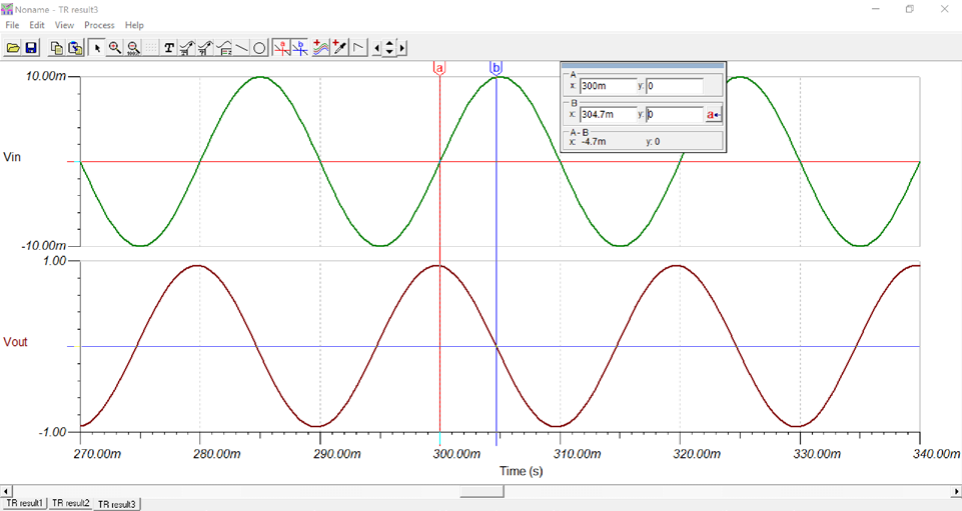

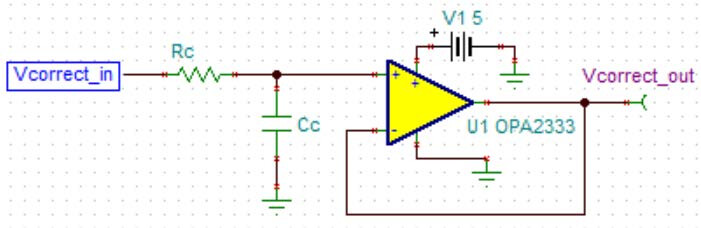

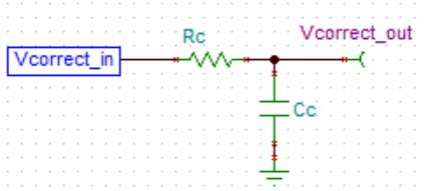

2.4.3 Hiệu chỉnh pha tần số thấp

Dựa trên phân tích ở trên, mạch tích phân có một sai số pha nhất định, tần số càng thấp thì sai số pha càng lớn. Lấy mạch trong Hình 8 làm ví dụ, tại tần số làm việc 50Hz, kết quả mô phỏng dạng sóng như Hình 13所示. Trong đó đường màu xanh lá là tín hiệu đầu vào, đường màu đỏ là tín hiệu đầu ra tích phân.

Hình 13 Phân tích pha dạng sóng mô phỏng mạch tích phân nghịch đảo

Về lý thuyết, đối với tín hiệu sin 50Hz thực hiện tích phân nghịch đảo, điểm qua zero của dạng sóng sau tích phân phải trễ pha 90° so với tín hiệu đầu vào, biểu hiện trong miền thời gian là điểm b trễ điểm a 5ms. Tuy nhiên từ Hình 13 có thể thấy, khoảng thời gian giữa hai điểm a và b là 4.7ms, chuyển đổi thành góc pha khoảng 84.6°. Tức là dạng sóng đầu ra tích phân nhanh pha khoảng 5.4° so với thiết kế dự kiến. Nói chung, có hai trường hợp cần xem xét nghiêm túc vấn đề hiệu chỉnh pha. Một là hệ thống có yêu cầu cao về pha, như điều khiển đóng cắt cầu dao, pha không chính xác sẽ tạo ra hồ quang lớn, đe dọa an toàn thiết bị và con người; hai là tần số làm việc của hệ thống thấp, như đối với doanh nghiệp điện lực, tần số công nghiệp (50/60 Hz) là ứng dụng chính, tần số thấp gây ra sai số pha lớn.

Phân tích cơ chế sinh ra sai số pha và biện pháp hiệu chỉnh. Sai số pha của mạch tích phân:

Nếu sử dụng mạch hiệu chỉnh lệch, cũng sẽ sinh ra một sai số pha khác:

\varphi_1 và \varphi_2 đều sinh ra pha nhanh, do đó cần một mắc hiệu chỉnh chậm pha để triệt tiêu, như Hình 14所示. Hiệu chỉnh pha chủ yếu chia thành hai loại có nguồn và không nguồn. Hiệu chỉnh có nguồn cho hiệu quả tốt nhất, không bị ảnh hưởng bởi trở kháng tải, nhưng cần thêm một op-amp, chi phí cao hơn; hiệu chỉnh không nguồn chi phí rất thấp, nhưng hiệu quả hiệu chỉnh bị ảnh hưởng bởi trở kháng tải, thường dựa vào yêu cầu ứng dụng để quyết định sử dụng giải pháp nào. Để đảm bảo hiệu quả hiệu chỉnh tốt, tụ của mạch tích phân và hiệu chỉnh tần số thấp nên chọn loại C0G hoặc NP0.

Hình 14 Hình bên trái là hiệu chỉnh pha có nguồn, hình bên phải là hiệu chỉnh pha không nguồn

3 Kiểm tra hệ thống

3.1 Kiểm tra hiệu năng

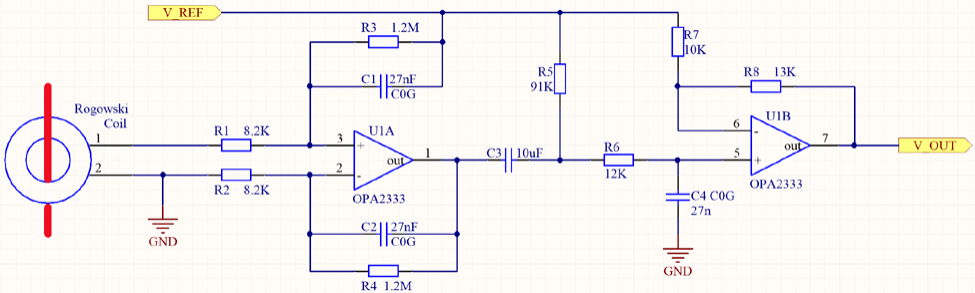

Lấy ứng dụng tần số công nghiệp 50Hz làm ví dụ, thiết kế mạch tích phân nguồn đơn như Hình 15所示. Mục tiêu thiết kế dự kiến là điện áp đầu ra thay đổi tuyến tính với dòng điện đầu vào, hệ số tỷ lệ là 52.4. Trong đó thông số thiết kế của cuộn dây Rogowski là 101nH.

Hình 15 Sơ đồ nguyên lý mạch tích phân nguồn đơn cho ứng dụng tần số công nghiệp

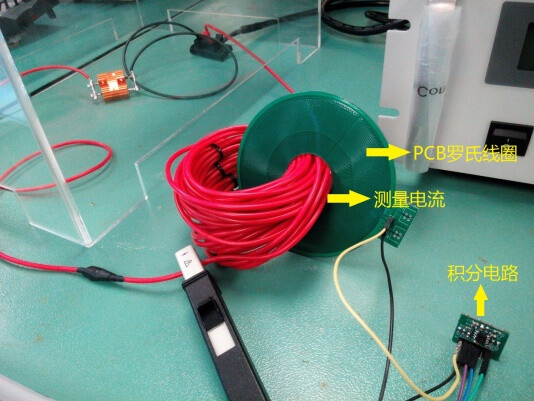

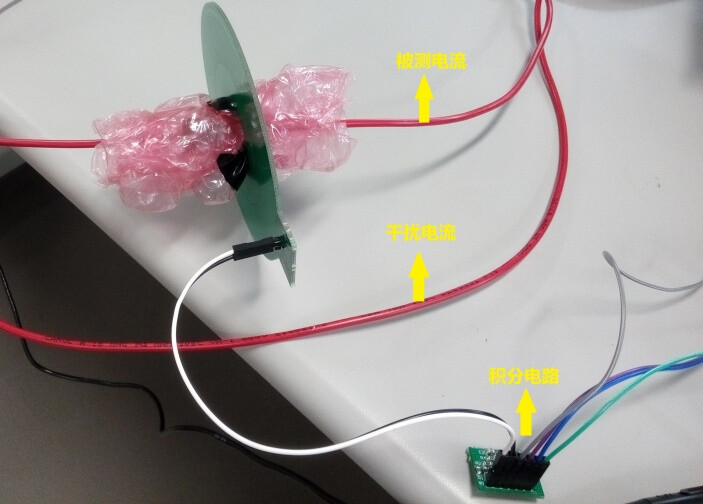

Đặt dây dẫn dòng điện đi qua thẳng góc cuộn dây Rogowski PCB, do thiết bị đo bị giới hạn nên dòng điện đầu ra nhỏ, do đó đã tăng số vòng, môi trường đo và dạng sóng như Hình16所示.

Hình 16 Hình bên trái là môi trường đo, hình bên phải là dạng sóng đo (phần màu tím là dòng điện, phần màu vàng là điện áp đầu ra tích phân)

Từ Hình 16 bên phải có thể thấy, dạng sóng điện áp đầu ra cơ bản phù hợp với dạng sóng dòng điện, đạt được hiệu quả đo tốt. Dữ liệu đo được tổng hợp như Bảng 1.

Bảng 1 Dữ liệu đo cuộn dây Rogowski PCB

| Dòng điện đầu vào(RMS)/A | Điện áp đầu ra(RMS)/mV | Dòng điện đầu vào(RMS)/A | Điện áp đầu ra(RMS)/mV |

|---|---|---|---|

| 0.46 | 20.95 | 2.74 | 124.8 |

| 0.92 | 42.03 | 3.26 | 148.0 |

| 1.39 | 63.02 | 3.68 | 166.8 |

| 1.83 | 83.70 | 4.01 | 185.4 |

| 2.30 | 104.6 | 4.46 | 202.5 |

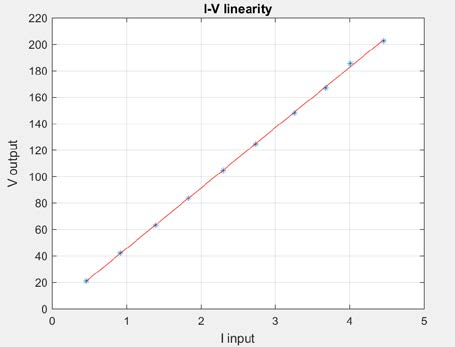

Thực hiện nội suy tuyến tính dữ liệu Bảng 1, như Hình17所示. Kết quả cho thấy tuyến tính giữa điện áp đầu ra và dòng điện đầu vào rất tốt, gần như thoả mãn quan hệ sau:

Hình 17 Nội suy tuyến tính điện áp đầu ra và dòng điện đầu vào

Theo tính toán lý thuyết, quan hệ giữa điện áp đầu ra và dòng điện đầu vào là:

Hệ số kết quả đo 45.64 nhỏ hơn một chút so với kết quả lý thuyết 47.21, nhưng sai số được kiểm soát trong 5%, cơ bản phù hợp với mục tiêu thiết kế dự kiến.

3.2 Phân tích sai số và cải tiến kiểm tra hiệu năngSai số thử nghiệm chủ yếu liên quan đến vị trí tương đối giữa dây dẫn mang dòng điện và cuộn dây. Để giảm thiểu sai số, thông thường yêu cầu dây dẫn mang dòng điện dài hơn phải đi qua vuông góc qua tâm của cuộn dây Rogowski và cố gắng giảm thiểu độ uốn cong của dây. Do hạn chế của thử nghiệm này là dòng điện đo nhỏ, nên đã áp dụng phương pháp tăng số vòng dây để nâng cao hệ số tư cảm tương đương của cuộn dây, do đó dây dẫn mang dòng điện không hoàn toàn đi qua tâm cuộn dây và tồn tại độ uốn cong dây cáp lớn, vì vậy hệ số tư cảm thực tế của cuộn dây nhỏ hơn giá trị lý thuyết, nhưng sự khác biệt không lớn, cơ bản phù hợp với mục tiêu thiết kế.

3.3 Kiểm tra nhiễu

Khi cuộn dây Rogowski đo dòng điện, yêu cầu dòng điện được đo phải đi qua lỗ xuyên tâm của cuộn dây. Tuy nhiên trong môi trường làm việc thực tế, xung quanh dòng điện được đo thường còn có các dòng điện xoay chiều khác (như trong trường hợp truyền tải điện xoay chiều ba pha). Dựa trên nguyên lý làm việc của cuộn dây Rogowski, dòng điện xoay chiều bên ngoài cũng có thể tạo ra từ trường biến thiên trong cuộn dây, gây nhiễu cho dòng điện được đo. Do đó việc phân tích khả năng chống nhiễu của cuộn dây Rogowski đối với các dòng điện xung quanh là cần thiết.

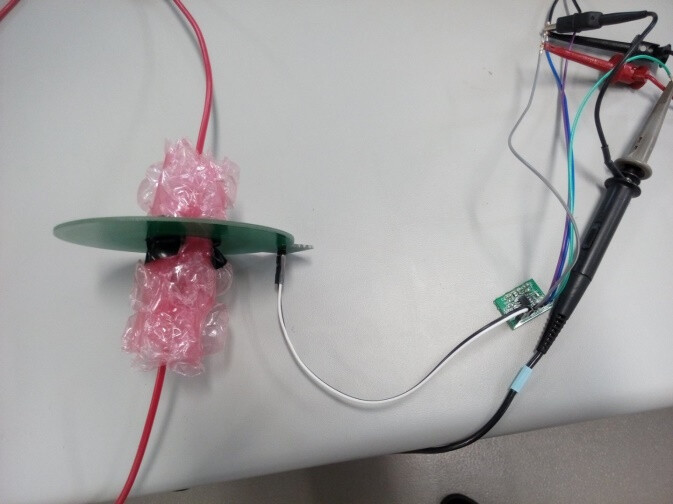

Quy trình cơ bản của kiểm tra nhiễu là trước tiên đo mối quan hệ tương ứng giữa điện áp đầu ra và dòng điện được đo trong điều kiện không có dòng nhiễu. Sau đó thêm dòng nhiễu xung quanh dòng điện được đo (tức là bên ngoài cuộn dây), kiểm tra xem điện áp đầu ra tích phân có thay đổi hay không khi cùng một dòng điện được đo. Dựa trên giả định này, môi trường đo lường cho kiểm tra nhiễu của cuộn dây Rogowski như Figure18.

Figure 18 Hình bên trái là môi trường đo không có dòng nhiễu, hình bên phải là môi trường đo có dòng nhiễu

Do hạn chế của hiện trường đo không thể cung cấp dòng nhiễu lớn, để đạt hiệu quả nhiễu tốt hơn, dòng điện được đo không tăng số vòng dây và làm cho dòng nhiễu có giá trị tương đương với dòng điện được đo. Để bù cho số vòng dây, trong kiểm tra nhiễu đã tăng hệ số khuếch đại của mạch tích phân (R7 trong Figure15 được thay đổi thành 100Ω). Cần lưu ý rằng hệ số khuếch đại quá lớn sẽ mang lại một số bất lợi, như offset đầu ra tăng lên và độ lệch giữa độ lợi thực tế của hệ số khuếch đại so với giá trị thiết kế tăng lên, v.v. Do đó trong ứng dụng thực tế không nên chọn hệ số khuếch đại lớn. Tuy nhiên trong kiểm tra chống nhiễu này, chúng ta quan tâm nhiều hơn đến ảnh hưởng của tín hiệu nhiễu đối với tín hiệu được đo khi mạch được cố định, vì vậy ảnh hưởng của hệ số khuếch đại lớn không đáng kể.

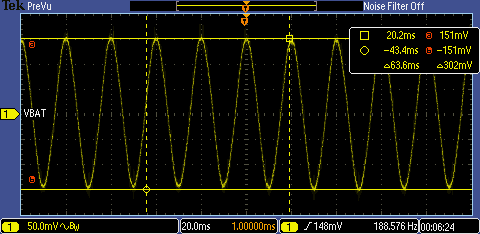

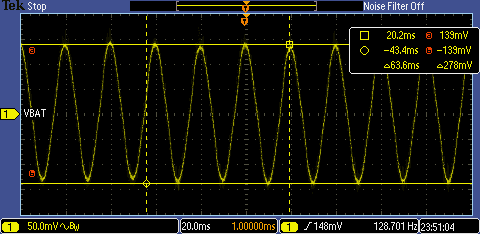

Trong điều kiện có và không có dòng nhiễu, dạng sóng điện áp đầu ra tích phân được đo như Figure19.

Figure 19 Hình bên trái là dạng sóng điện áp đầu ra không có dòng nhiễu, hình bên phải là dạng sóng điện áp đầu ra có dòng nhiễu

Tiếp theo, dữ liệu thử nghiệm được sắp xếp như Table2.

Table 2 Dữ liệu kiểm tra nhiễu

| Dòng điện được đo (RMS)/A | Dòng nhiễu (RMS)/A | Điện áp đầu ra khi không có dòng nhiễu (RMS)/mV | Điện áp đầu ra khi không có dòng nhiễu (RMS)/mV | Sai số% |

|---|---|---|---|---|

| 0.41 | 0.41 | 21.9 | 20.6 | -5.9% |

| 0.82 | 0.81 | 43.1 | 38.9 | -9.7% |

| 1.23 | 1.22 | 65.1 | 58.5 | -10.1% |

| 1.64 | 1.63 | 83.4 | 78.5 | -5.9% |

| 2.06 | 2.04 | 106.1 | 98.3 | -7.4% |

Từ Table2 có thể thấy, việc đưa dòng nhiễu vào làm suy giảm biên độ điện áp đầu ra, gây ra sai số đo lường. Trong thử nghiệm này, sai số khoảng 10%.

3.4 Phân tích sai số và cải tiến kiểm tra nhiễu

Khi có dòng nhiễu bên ngoài cuộn dây Rogowski, do sự thay đổi của dòng nhiễu tạo ra từ trường biến thiên, từ trường biến thiên này tạo ra điện thế cảm ứng trong cuộn dây Rogowski, đây là nguyên nhân gốc rễ của sai số đo lường. Mức độ sai số đo lường liên quan đến giá trị dòng nhiễu và cũng liên quan đến khoảng cách giữa dòng nhiễu và dòng điện được đo. Trong thử nghiệm này, tín hiệu nhiễu rất lớn, tương đương với tín hiệu được đo, và khoảng cách giữa tín hiệu nhiễu và cuộn dây Rogowski ngắn, do đó gây ra sai số đo lường lớn. Trong đo lường thực tế, cần chú ý đặt dòng nhiễu xa cuộn dây Rogowski, khi điều kiện cho phép thì giảm dòng nhiễu để có thể giảm sai số đo lường.

4 Tài liệu tham khảo

- TI-Design-01063, High Accuracy AC Current Measurement Reference Design Using PCB Rogowski Coil Sensor, Texas Instruments Inc.

- OPA2333 datasheet 2016, Texas Instruments Inc.