본 문서는 TI 애플리케이션 노트 문서(ZHCA710 – Jun. 2017)에서 인용되었습니다.

저자: Wiky Liao / Kevin Zhang

PDF 문서 다운로드 링크: https://www.123865.com/s/2Y9Djv-1uTdH

요약

PCB 로고프스키 코일은 응답 속도가 빠르고 선형도가 우수하며 비용이 저렴하다는 특징으로 인해 교류 대전류 환경, 예를 들어 교류 전동기 제어, 에스컬레이터, 가공선 및 케이블 등에서 광범위하게 적용되고 있습니다. 로고프스키 코일의 출력 신호는 원래 전류의 미분이므로 적분 회로를 함께 설계해야 합니다. 본 문서는 PCB 로고프스키 코일의 작동 원리 및 설계 포인트를 상세히 소개하고, TI의 OP 앰프 OPA2333을 사용하여 고성능 적분 회로를 설계하는 방법을 설명합니다. 이를 통해 고객이 응용 요구사항에 부합하는 PCB 로고프스키 코일 전류 검출 솔루션을 신속하게 설계할 수 있도록 돕습니다.

1 로고프스키코일

1.1 로고프스키 코일 개요

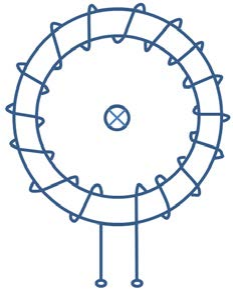

로고프스키 코일은 비접촉식 전류 센서로, 주로 유연성과 경성의 두 가지 대분류로 나뉘며, PCB 로고프스키 코일은 경성 로고프스키 코일에 속합니다. 그 구조적 특징은 도선이 비자성 링형 프레임 위에 균일하게 감겨 링형 코일을 형성하고, 측정 대상 전류가 코일 중심을 통과하는 것으로, Figure 1과 같습니다.

Figure 1 왼쪽 그림은 로고프스키 코일 구조 개요도이고, 오른쪽 그림은 PCB 로고프스키 코일 레이아웃입니다.

1.2 로고프스키 코일 작동 원리

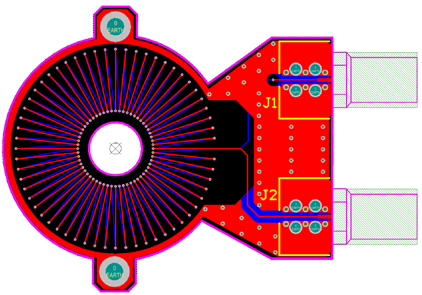

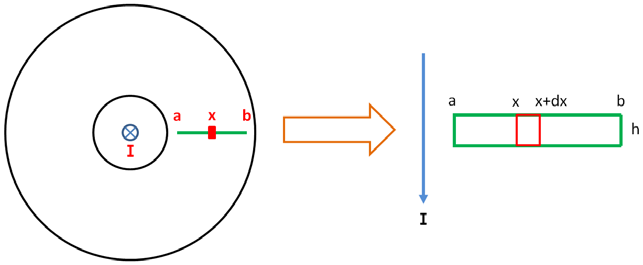

무한히 긴 전류를 흐르는 도선이 로고프스키 코일 중심에 수직으로 통과한다고 가정하고, 도선 전류는 I입니다. 코일 내경은 a, 외경은 b, 판 두께는 h, PCB 도선의 투자율은 μ입니다. Figure 2와 같습니다.

Figure 2 로고프스키 코일 분석 모델, 왼쪽 그림은 평면도이고, 오른쪽 그림은 단면도입니다.

비오-사바르 법칙에 따르면, x에서의 자기 유도 세기:

상층 도선과 하층 도선은 비아를 통해 연결되어 1 권을 구성하며, 매 권이 발생하는 자속량:

렌츠 법칙에 따라, N 권 코일에서 유기된 전압:

식(3)에서, M는 상호 인덕턴스 계수입니다.

식(3)에 따르면, 로고프스키 코일의 출력은 전압으로 측정 전류와 미분 관계를 가지므로, 로고프스키 코일은 교류 전류 측정에만 적용되며, 사용 시 적분기와 함께 사용해야 합니다.

1.3 PCB 로고프스키 코일 설계 요점

1.3.1 권수 제한

로고프스키 코일의 주요 매개변수는 상호 인덕턴스 계수 M이며, 그 값은 주로 권수, 판 두께, 코일 내경 및 외경과 관련이 있습니다. 그중에서 PCB 비아 크기와 제조 수준에 제한을 받아, 실제 권수는 무한히 클 수 없으며, 일정한 제한이 있습니다. 권수 계산 모델은 Figure 3과 같습니다.

비아 V1과 V2 사이의 거리:

제조 수준에 제한을 받아, 이 두 인접 비아 사이의 거리는 적어도 3배 이상의 패드와 비아 지름 차이보다 커야 하며, 즉:

여기서 $V_p$는 비아의 패드 지름이고, $V_h$는 비아 지름입니다.

식(4)와(5)로부터 두 연결 비아의 각도를 도출할 수 있습니다:

따라서 PCB 로고프스키 코일의 최대 권수:

일반적으로, 판 두께도 최소 비아 크기를 결정하므로, 코일을 설계하기 전에 PCB 제조업체와 확인하는 것이 좋습니다.

1.3.2 공간의 합리적 이용

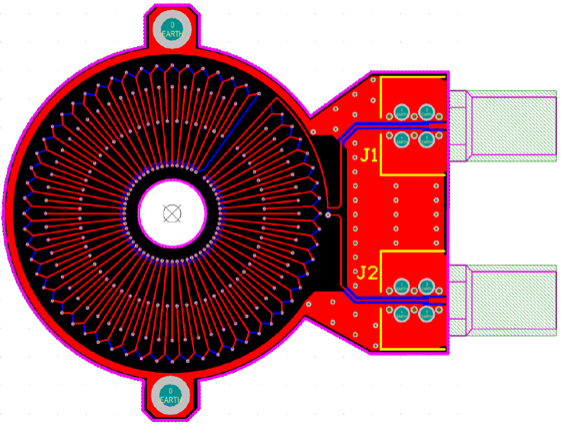

PCB 로고프스키 코일은 일반적으로 방사형 배선을 하여, 외측 부근의 선 권선 사이에 큰 공간이 생깁니다. 따라서 큰 권선 사이에 작은 권선을 추가할 수 있으며, 이렇게 하면 판 크기가 변하지 않는 상태에서 코일의 상호 인덕턴스 계수를 증가시킬 수 있습니다. Figure 4와 같습니다. 작은 권선의 내경을 c, 외경을 $d$라고 하면, 코일의 상호 인덕턴스 계수:

Figure 4 작은 권선을 추가한 로고프스키 코일

판 크기가 고정된 경우, 매우 큰 상호 인덕턴스 계수가 필요하다면, 여러 개의 PCB 로고프스키 코일을 시리즈 연결하는 것을 고려할 수 있습니다. 즉, Figure 4의 J2 출력을 다음 PCB 코일의 J1에 연결하여 신호 중첩을 실현합니다.

2 적분 회로 설계

2.1 이상 적분 회로의 부족점 및 개선

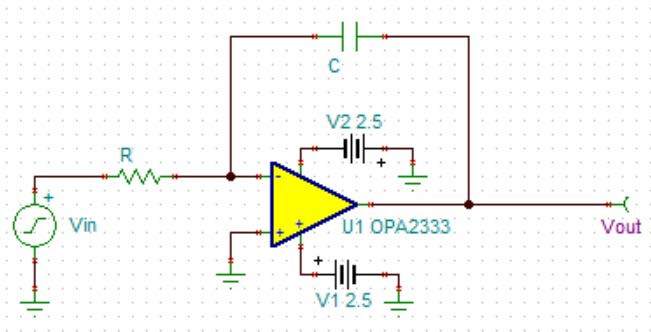

로고프스키 코일의 출력 전압은 측정 전류 신호의 미분이므로, 후단에 적분 회로가 없다면 전류에 약간의 고주파 성분만 있어도 코일 출력단에서 높은 전압이 유기되어 기본파 신호를 묻어버립니다. 따라서 후단에는 적분 회로가 필요하여 신호를 복원합니다. 이상 적분 회로는 Figure 5와 같습니다.

Figure 5 왼쪽 그림은 이상 적분 회로의 원리도이고, 오른쪽 그림은 적분 출력 전압 파형입니다.

입력 신호의 오프셋이 0일 때, 적분 출력 후의 파형 오프셋도 0이어야 합니다. 그러나 위 그림에서 보듯이, 적분 출력 전압의 오프셋은 0이 아니며, 파형이 전원 레일로 드리프트되었습니다. 실제 OP Amp 작동 시 상황은 더 심각하여, 파형이 전원 레일에서 클리핑이 발생하여 포화 왜곡 또는 차단 왜곡을 일으킵니다. 그 주요 원인은 현재의 OP Amp가 모두 이상 OP Amp가 아니며, 고유의 오프셋 전압 offset이 존재하기 때문입니다. 다른 회로가 없으므로, offset은 적분 커패시터를 충전하게 되며, 장시간 경우에는 필연적으로 커패시터 포화를 유발하여 클리핑을 일으킵니다. 따라서 적분 커패시터 양단에 병렬 저항을 연결하여 커패시터에 방전 회로를 제공해야 하며, 회로가 안정적으로 작동하도록 합니다. Figure 6과 같습니다. 병렬 저항 연결 후, 회로의 적분 성능을 분석할 필요가 있습니다.

Figure 6 적분 회로 병렬 저항 연결 후 성능 분석

OP Amp의 반상 입력단에서 키르히호프 전류 방정식을 세우면:

식(9)는 1차 비선형 동차 방정식으로, 이를 풀면:

여기서 $C_1$은 상수입니다. 입력 신호 $V_{in} = \cos(\omega t)$라고 가정하면, 식(10)은 다음과 같이 간소화될 수 있습니다:

주파수 영역 관점에서, 병렬 저항 연결 후 회로의 증폭 배수:

식(11)과(12)는 두 가지 중요한 정보를 전달합니다:

- 시간 $t$가 점점 커질수록, 출력단 전압 $V_{out}$의 지수 부분 $C_1 e^{-\frac{t}{R_f C}}$는 점점 작아지며, 최종적으로 완전히 무시할 수 있습니다;

- $R_f \gg \frac{1}{\omega C}일 때, \varphi \approx 0^\circ$이며, 증폭 배수는 이상적인 $\frac{1}{\omega RC}$에 가까워지며, 이 때 출력단 전압이 입력 신호의 반상 적분이라고 간주할 수 있습니다.

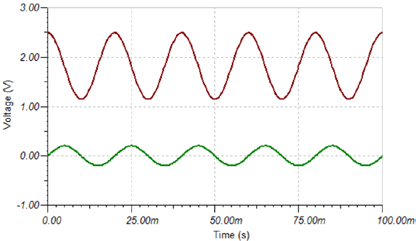

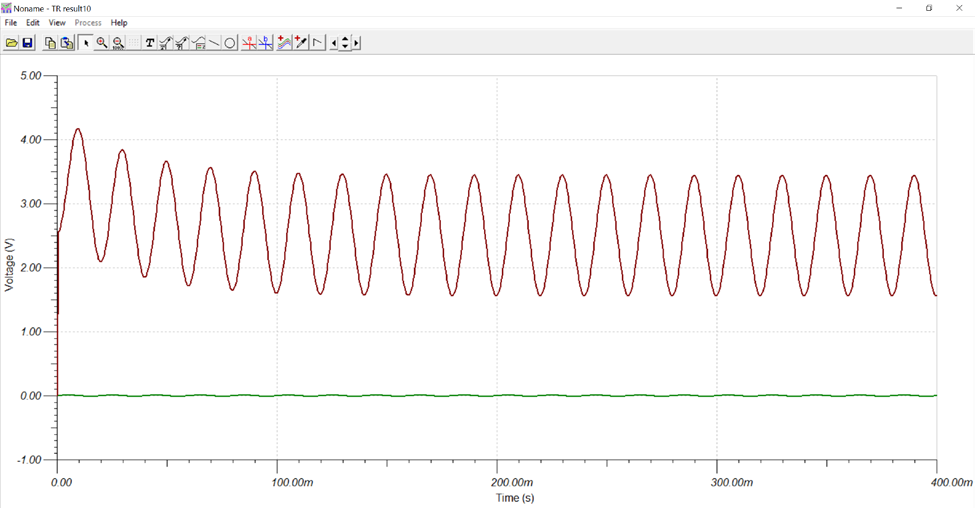

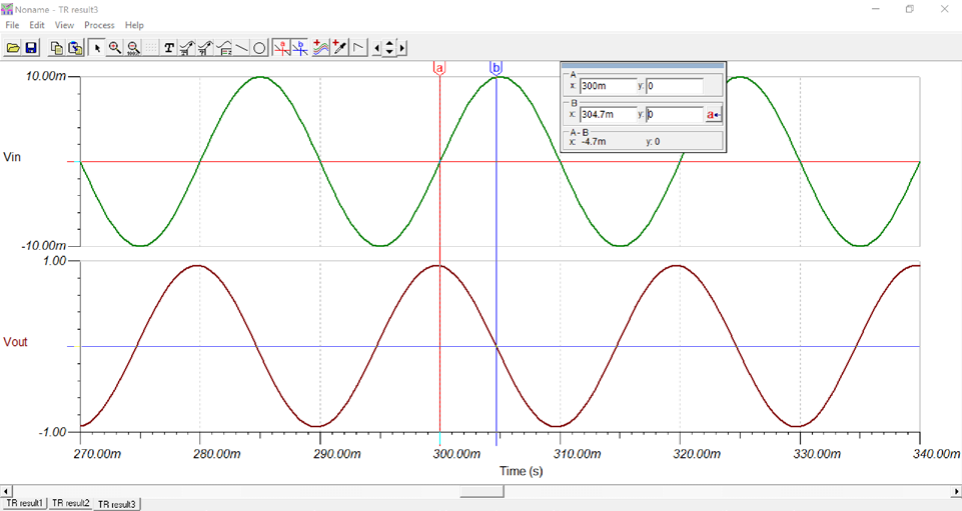

이상 분석에 따르면, 적분 회로 시뮬레이션 결과는 Figure 7과 같습니다. 여기서 녹색 곡선은 입력이고, 빨간색 곡선은 출력입니다. 출력 신호는 초기 단계에서 지수 인자의 영향으로 변동이 발생했지만, 최종적으로 안정되어 적분 효과가 매우 좋습니다.

Figure 7 병렬 저항 연결 후 적분 회로 시뮬레이션 파형

2.2 적분 회로 OP Amp 선택

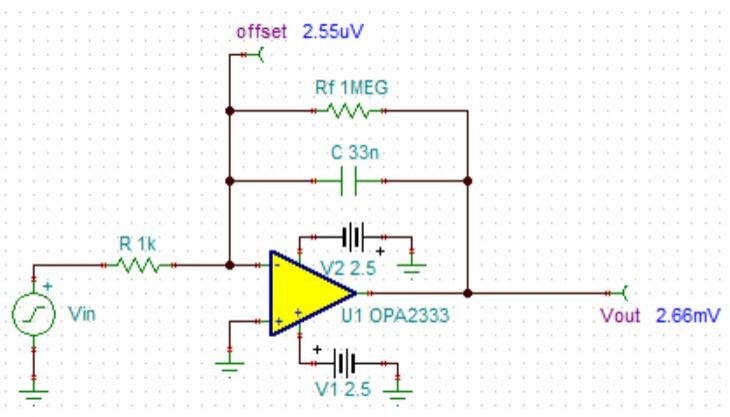

좋은 적분 효과를 얻으려면 일반적으로 피드백 저항 Rf를 가능한 한 크게 선택해야 하지만, 그렇다고 해서 무조건 크게 선택하는 것이 좋은 것은 아닙니다. 그 주요 원인은 적분 회로가 OP Amp offset에 대해 동상 증폭 회로이기 때문에, 피드백 저항 Rf가 너무 크면 출력단에 큰 DC 오프셋이 존재하여 적분 드리프트 억제 능력이 약화됩니다. 따라서 적분 회로 내의 OP Amp는 매우 작은 offset 값을 가져야 하며, 출력단의 DC 레벨을 가능한 한 낮게 유지해야 합니다. OPAx333은 TI에서 출시한 Zero Drift 기능을 갖춘 저 offset OP Amp로, 내부에서 디지털 보정 방법을 사용하여 offset과 드리프트 전압을 크게 낮췄으며, offset 최대값은 10μV에 불과하고, 0.05μV/°C에 이르는 낮은 드리프트를 동시에 가지고 있어 적분 회로 설계에 매우 적합합니다. Figure 8은 OPA2333 적분 회로의 DC 시뮬레이션을 수행한 것으로, 피드백 저항이 적분 저항의 1000배인 경우에도 출력이 2.66mV에 불과하여 성능이 매우 우수합니다. 동시에 OPAx333의 최대 정적 전류는 25μA에 불과하며, 저전력 고성능 연산 증폭기입니다.

Figure 8 OPA2333 적분 회로 DC 시뮬레이션

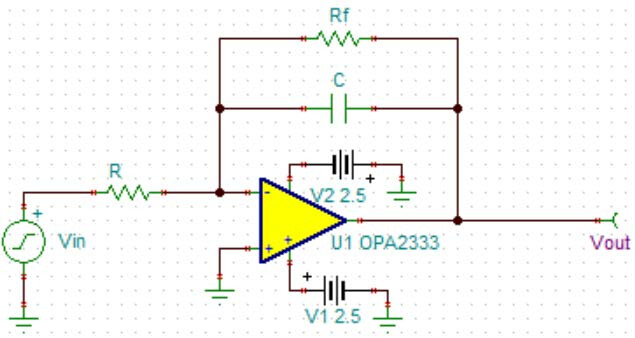

2.3 단일 전원 적분 회로 설계

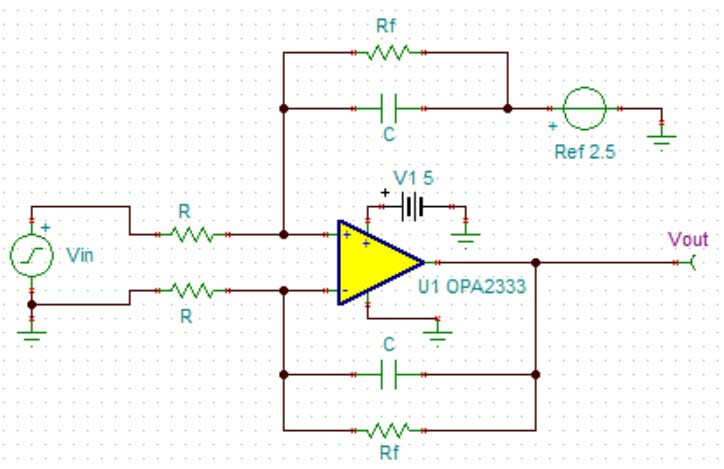

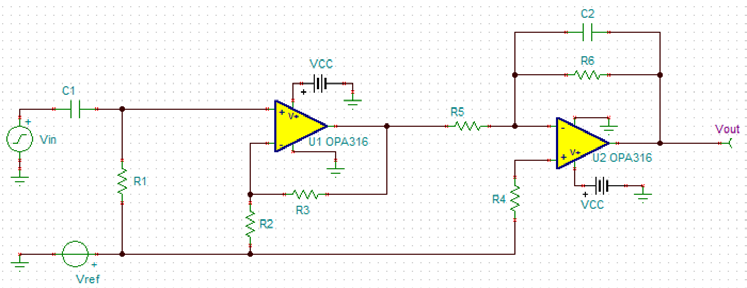

앞서 언급한 적분 회로는 이중 전원 적분 방식을 채택했지만, 많은 고객의 응용 분야는 단일 전원 공급만 지원하므로, 단일 전원 적분 회로를 설계할 필요가 있습니다. 차동 OP Amp의 회로 구조를 참고하여, Figure 9와 같이 단일 전원 적분 회로를 설계합니다.

Figure 9 단일 전원 적분 회로

앞서의 분석 방법과 유사하게, 입력 전압 $V_{in} = \cos(\omega t)$라고 가정하면, 출력 전압:

식(13)의 핵심 해석:

- 출력 특성: 출력 전압은 입력 신호의 동상 적분이며, 동시에 DC 오프셋 $V_{ref}$를 포함합니다;

- 시뮬레이션 검증: 시뮬레이션 출력 파형은 Figure 10에 해당하며, 여기서 녹색 곡선은 입력 신호이고, 빨간색 곡선은 출력 신호이며, 시스템의 적분 성능이 양호하게 나타납니다.

Figure 10 단일 전원 적분 회로 시뮬레이션 파형

2.4 고성능 적분 회로 주의사항

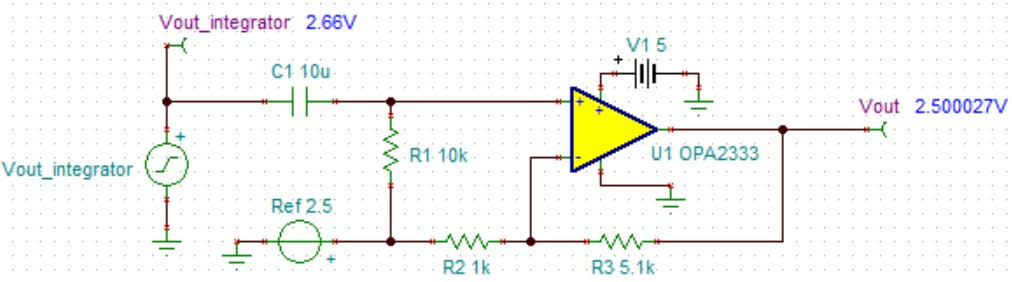

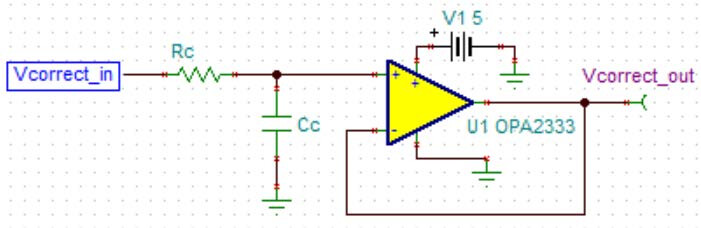

2.4.1 오프셋 보정

앞서 회로 분석에서 알 수 있듯이, 출력단 전압 오프셋에는 일정한 오차가 존재하며, OPAx333 OP Amp의 경우 최대 몇 mV에 불과합니다(성능이 좋지 않은 OP Amp의 경우 수백 mV에 이를 수 있습니다). 출력단 오프셋 요구사항이 높다면, 오프셋을 다시 보정할 필요가 있으며, 보정 회로는 적분 회로의 후단에 위치합니다. Figure 11과 같습니다. 시뮬레이션 결과에서 알 수 있듯이, 출력단 Vout의 DC 오프셋과 사전 설정된 Ref 값 사이의 차이는 27μV에 불과하여 오프셋 효과가 매우 우수합니다. 동시에 비반상 비율 저항 R2와 R3는 신호를 추가로 조정하여 출력이 풀 스윙에 도달하도록 할 수 있습니다.

Figure 11 오프셋 보정 회로 및 DC 시뮬레이션 결과

2.4.2 고주파 고장 성분 측정

일부 응용 분야(예: AFCI)에서 사용자는 주로 전류의 고주파 고장 성분에 관심을 가지며, 고장 상황에서 적절한 동작(예: 회로 차단)을 수행하기 위함이며, 이 때 저주파 대역의 정상 작동 전류는 그다지 중요하지 않으며, 심지어 무시할 수 있습니다. 이러한 응용 상황에 대해 먼저 고역 필터를 설정하여 저주파 성분을 필터링할 수 있습니다. 그 다음 증폭 회로를 추가하여 고주파 성분 신호를 증폭시켜 적분 후의 신호가 충분히 모니터링될 수 있도록 보장하며, 응용 회로는 Figure 12와 같습니다.

Figure 12 고주파 고장 성분 측정 회로

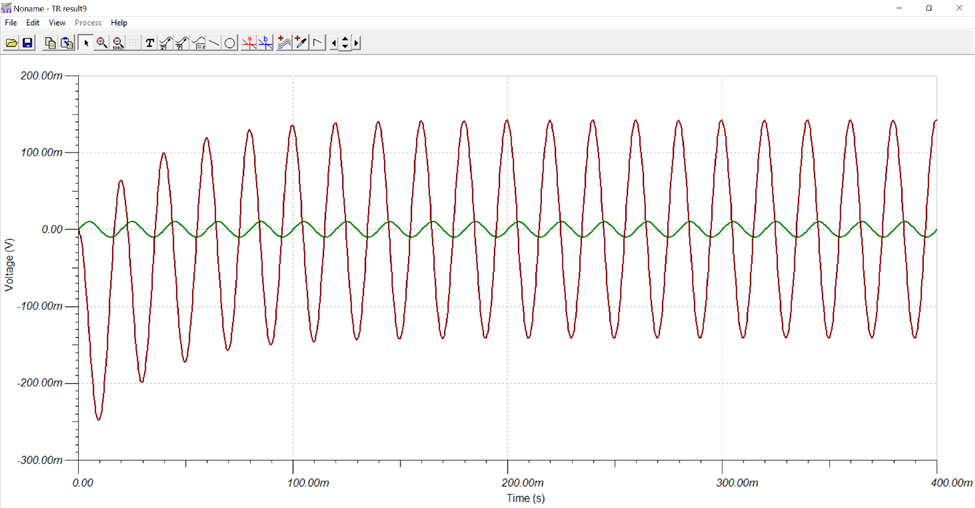

2.4.3 저주파 위상 보정

앞서 분석에 따르면, 적분 회로에는 일정한 위상각 오차가 존재하며, 주파수가 낮을수록 위상각 오차가 커집니다. Figure 8의 회로를 예로 들어, 50Hz의 작동 주파수에서 시뮬레이션 파형 결과는 Figure 13과 같습니다. 여기서 녹색 곡선은 입력이고, 빨간색 곡선은 적분 출력입니다.

Figure 13 반상 적분 회로 시뮬레이션 파형 위상 분석

이론적으로, 50Hz의 정현파에 대해 반상 적분을 수행하면, 적분 후 파형의 영점 교차점은 입력 신호보다 90° 지연되어야 하며, 시영역에서 나타나는 효과는 b점이 a점보다 5ms 지연되는 것입니다. 그러나 Figure 13에서 알 수 있듯이, a와 b 두 점 사이의 시간 차이는 4.7ms이며, 위상각으로 변환하면 약 84.6°입니다. 즉, 적분 출력 파형이 예상 설계보다 약 5.4° 위상각만큼 선행했다는 의미입니다. 일반적으로 두 가지 경우에서 위상 보정 문제를 중점적으로 고려해야 합니다. 하나는 시스템이 위상 요구사항이 높은 경우로, 예를 들어 차단기의 개폐를 제어하는 경우, 위상이 정확하지 않으면 큰 아크를 발생시켜 장비와 인체 안전을 위협합니다. 두 번째는 시스템 자체의 작동 주파수가 낮은 경우로, 예를 들어 전력 기업의 경우, 공업 주파수(50/60 Hz)가 주요 응용 분야이며, 저주파는 큰 위상각 오차를 가져옵니다.

아래에서 위상각 오차 발생 기구 및 보정 조치를 분석합니다. 적분 회로의 위상각 오차:

오프셋 보정 회로를 채택했다면, 또 다른 위상각 오차가 발생합니다:

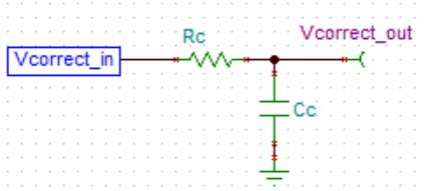

$\varphi_1$과 $\varphi_2$는 모두 선행 위상각을 발생시키므로, 이를 상쇄하기 위해 지연 보정 단계가 필요합니다. Figure 14와 같습니다. 위상 보정은 주로 유원과 무원의 두 가지 유형으로 나뉩니다. 유원 보정은 효과가 가장 좋으며, 부하 임피던스의 영향을 받지 않지만, 추가로 OP Amp가 필요하여 비용이 높습니다. 무원 보정은 비용이 매우 낮지만, 보정 효과는 부하 임피던스의 영향을 받으며, 일반적으로 응용 요구사항에 따라 어느 방식을 채택할지 결정합니다. 보다 나은 보정 효과를 보장하기 위해, 적분 회로와 저주파 보정 회로의 커패시터는 가능한 한 C0G 또는 NP0 시리즈를 선택하는 것이 좋습니다.

Figure 14 왼쪽 그림은 유원 위상 보정이고, 오른쪽 그림은 무원 위상 보정입니다.

3 시스템 테스트

3.1 성능 테스트

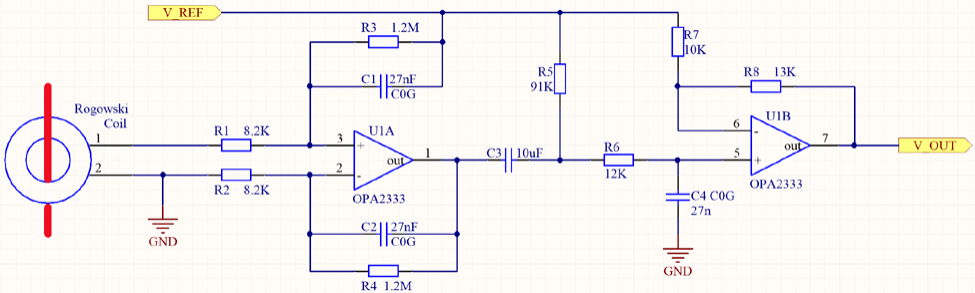

공업 주파수 50Hz 응용 분야를 예로 들어, Figure 15와 같이 단일 전원 적분 회로를 설계합니다. 예상 설계 목표는 출력단 전압이 입력 전류와 선형 변화하며, 비례 계수는 52.4입니다. 여기서 로고프스키 코일 설계 매개변수는 101nH입니다.

Figure 15 공업 주파수 응용 분야의 단일 전원 적분 회로 원리도

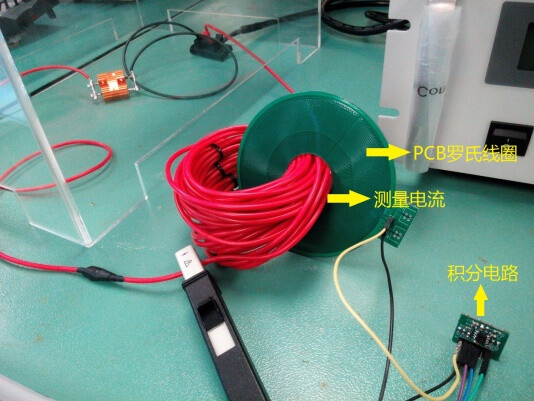

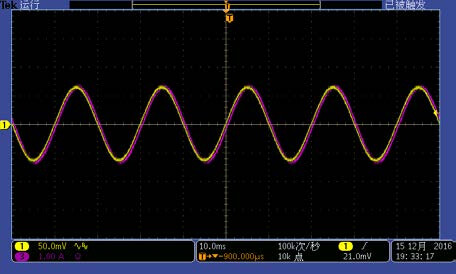

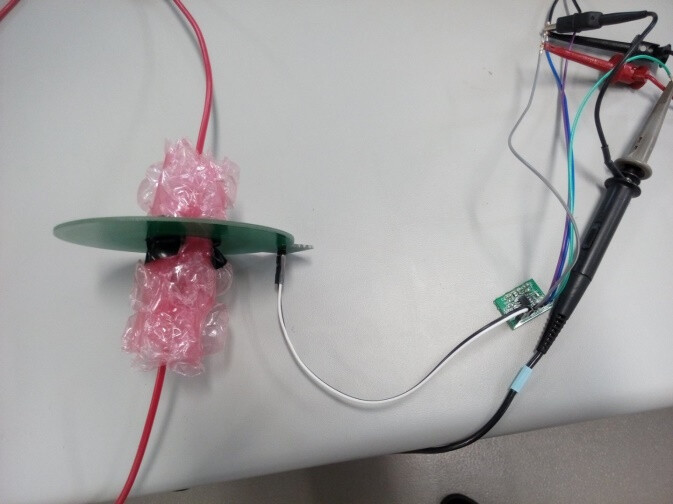

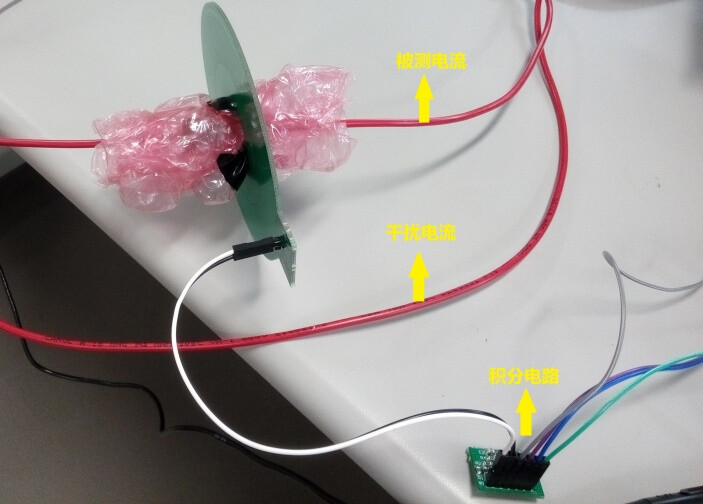

전류 도선을 PCB 로고프스키 코일에 수직으로 통과시키며, 측정 장비 출력 전류가 작으므로 권수를 증가시켰으며, 측정 환경 및 파형은 Figure16과 같습니다.

Figure 16 왼쪽 그림은 측정 환경이고, 오른쪽 그림은 측정 파형(보라색 부분은 전류, 노란색 부분은 적분 출력 전압)입니다.

Figure16 오른쪽 그림에서 알 수 있듯이, 출력단 전압 파형은 전류 파형과 기본적으로 일치하며, 비교적 좋은 측정 효과를 달성했습니다. 측정 데이터는 Table1과 같이 정리되었습니다.

Table 1 PCB 로고프스키 코일 측정 데이터

| 입력 전류(RMS)/A | 출력 전압(RMS)/mV | 입력 전류(RMS)/A | 출력 전압(RMS)/mV |

|---|---|---|---|

| 0.46 | 20.95 | 2.74 | 124.8 |

| 0.92 | 42.03 | 3.26 | 148.0 |

| 1.39 | 63.02 | 3.68 | 166.8 |

| 1.83 | 83.70 | 4.01 | 185.4 |

| 2.30 | 104.6 | 4.46 | 202.5 |

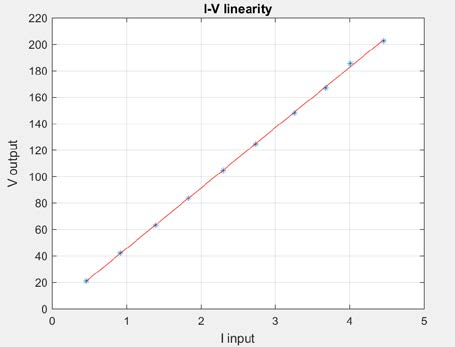

Table1 데이터에 대해 선형 근사를 수행하면, Figure17과 같습니다. 결과는 출력 전압과 입력 전류의 선형도가 매우 좋으며, 다음과 같은 관계식을 거의 만족하는 것으로 나타났습니다:

Figure 17 출력 전압과 입력 전류의 선형 근사

이론 계산에 따르면, 출력 전압과 입력 전류의 관계식은:

계수 측정 결과 45.64는 이론 결과 47.21보다 약간 작지만, 오차는 5% 이내로 제어되며, 기본적으로 예상 설계 목표에 부합합니다.

3.2 성능 테스트 오차 분석 및 개선측정 오차는 주로 전류를 흐르는 도선과 코일의 상대적 위치와 관련이 있다. 오차를 줄이기 위해 일반적으로 긴 전류 도선이 로고프스키 코일의 원심을 수직으로 통과하고, 선의 구부러짐을 가능한 한 줄이도록 요구된다. 본 테스트는 측정 전류가 작은 것으로 제한되었으므로 권선 수를 증가시켜 코일의 등가 상호인덕턴스 계수를 높이는 방법을 채택하였다. 따라서 전류 도선이 코일 원심을 모두 통과하지 않으며, 큰 케이블 구부러짐이 존재한다. 따라서 실제 측정된 코일 상호인덕턴스 계수가 이론값보다 작지만, 차이는 크지 않으며 설계 목표와 기본적으로 부합한다.

3.3 간섭 테스트

로고프스키 코일로 전류를 측정할 때, 측정 대상 전류가 코일 중심의 관통 구멍을 통과하도록 요구된다. 그러나 실제 작업 환경에서 측정 대상 전류 주변에는 일반적으로 다른 교류 전류(예: 3상 교류 전송 환경)가 존재한다. 로고프스키 코일의 작동 원리에 따르면 외부 교류 전류도 코일에서 교류 자기장을 발생시켜 측정 대상 전류를 간섭할 수 있다. 따라서 로고프스키 코일의 주변 전류에 대한 간섭 방지 능력을 분석하는 것이 필요하다.

간섭 테스트의 기본 과정은 먼저 간섭 전류가 없는 상태에서 출력 전압과 측정 대상 전류 간의 대응 관계를 측정하는 것이다. 그런 다음 측정 대상 전류 주변(즉, 코일 외부)에 간섭 전류를 추가하여 동일한 측정 대상 전류에서 적분 출력 전압이 변경되는지 검증한다. 이러한 구상에 따라 로고프스키 코일 간섭 테스트의 측정 환경은 Figure18과 같다.

Figure 18 왼쪽 그림은 간섭 전류 없는 측정 환경, 오른쪽 그림은 간섭 전류 있는 측정 환경

측정 현장에서 큰 간섭 전류를 제공할 수 없는 것으로 제한되었으므로, 더 나은 간섭 효과를 달성하기 위해 측정 대상 전류는 권선 수를 증가시키지 않았으며, 간섭 전류와 측정 대상 전류의 크기를 비슷하게 하였다. 권선 수에 대한 보상으로 간섭 테스트에서 적분 회로의 증폭 배수를 증가시켰다(Figure15의 R7를 100Ω로 변경). 설명이 필요한 점은 증폭 배수가 너무 크면 몇 가지 단점이 발생한다는 것이다. 예를 들어 출력 단의 오프셋이 커지고, 증폭 배수의 실제 이득과 설계값의 편차가 증가한다. 따라서 실제 적용 단계에서는 큰 증폭 배수를 선택하는 것이 바람직하지 않다. 그러나 본 간섭 방지 테스트에서는 회로가 고정된 상태에서 간섭 신호가 측정 신호에 미치는 영향에 더 관심이 있으므로, 큰 이득이 미치는 영향은 크지 않다.

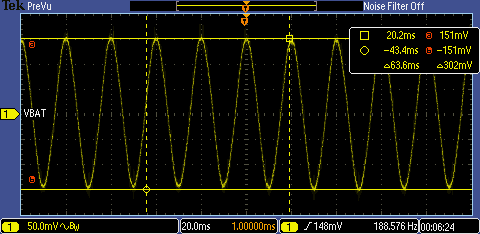

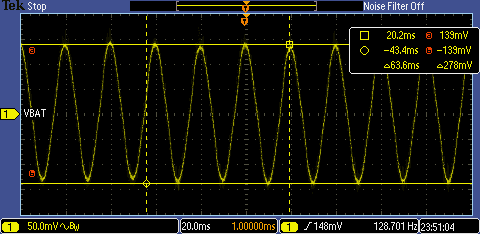

간섭 전류가 있을 때와 없을 때 측정된 적분 출력 전압 파형은 Figure19와 같다.

Figure 19 왼쪽 그림은 간섭 전류 없는 출력 전압 파형, 오른쪽 그림은 간섭 전류 있는 출력 전압 파형

테스트 데이터를 정리하면 Table2와 같다.

Table 2 간섭 테스트 데이터

| 측정 대상 전류(RMS)/A | 간섭 전류(RMS)/A | 간섭 전류 없을 때 출력 전압(RMS)/mV | 간섭 전류 있을 때 출력 전압(RMS)/mV | 오차% |

|---|---|---|---|---|

| 0.41 | 0.41 | 21.9 | 20.6 | -5.9% |

| 0.82 | 0.81 | 43.1 | 38.9 | -9.7% |

| 1.23 | 1.22 | 65.1 | 58.5 | -10.1% |

| 1.64 | 1.63 | 83.4 | 78.5 | -5.9% |

| 2.06 | 2.04 | 106.1 | 98.3 | -7.4% |

Table2에서 알 수 있듯이, 간섭 전류의 도입은 출력 전압의 진폭을 약화시켜 측정 오차를 유발한다. 본 테스트에서 오차는 10% 정도이다.

3.4 간섭 테스트 오차 분석 및 개선

로고프스키 코일 외부에 간섭 전류가 존재할 때, 간섭 전류의 변화로 인해 교류 자기장이 발생하고, 교류 자기장이 로고프스키 코일에서 유도 전위를 발생시키는 것이 측정 오차가 존재하는 근본 원인이다. 측정 오차의 크기는 간섭 전류 값과 관련이 있으며, 간섭 전류와 측정 대상 전류 간의 거리와도 관련이 있다. 본 테스트에서 간섭 신호는 매우 커서 측정 대상 신호 크기와 비슷했고, 간섭 신호와 로고프스키 코일의 거리가 짧아서 큰 측정 오차를 유발하였다. 실제 측정 시에는 간섭 전류를 로고프스키 코일에서 멀리 떨어뜨리고, 조건이 허용하는 경우 간섭 전류를 줄이면 측정 오차를 줄일 수 있다.

4 참고문헌

- TI-Design-01063, High Accuracy AC Current Measurement Reference Design Using PCB Rogowski Coil Sensor, Texas Instruments Inc.

- OPA2333 datasheet 2016, Texas Instruments Inc.