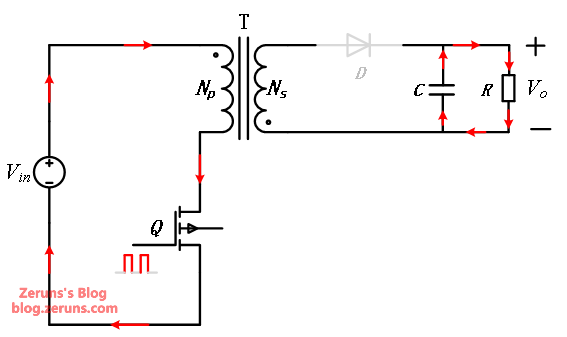

本記事では、入力電圧24V、出力電圧3A、出力電力72Wのフォワード型電源を例に、回路の各パラメータと部品選定を計算し、フォワード変圧器の計算方法と巻き方を解説します。

本記事の式は、インターネット上の資料を参考にしています。

記事内容に問題がある場合は、ご指摘いただけますと幸いです。

- 【ハードウェアオープンソース】24V3Aフォワード型スイッチング電源(UC3842ベース):https://blog.zeruns.com/archives/910.html

- 磁性素子/磁芯材料/磁芯構造の分析・比較・選定ガイド:https://blog.zeruns.com/archives/897.html

- 電子・マイコン技術交流QQグループ:2169025065

フォワード電源の動作パラメータ

まず、設計するフォワード電源のパラメータを明確に定義します。

| パラメータ | 値 |

|---|---|

| 定格入力電圧 V_{acnom} | 220VAC |

| 最低入力電圧 V_{acmin} | 85VAC |

| 最高入力電圧 V_{acmax} | 265VAC |

| 電源周波数 f_L | 50Hz |

| 出力電圧 V_{out} | 24V |

| 出力電流 I_{out} | 3A |

| 動作周波数 f_s | 150kHz |

| 設計効率 η | 85% |

フォワード電源の動作周波数は、特定のアプリケーション要件に基づいて設計者が自由に設定するものであり、固定値ではありません。 動作周波数を上げることで、変圧器、出力フィルタインダクタ、コンデンサの体積と重量を大幅に削減でき、電源全体の小型化が可能になります。これは高周波動作により小さな磁性素子やコンデンサを使用できるためです。しかし、周波数を上げるとスイッチング損失が増加し、電源効率の低下や発熱の悪化を招き、より複雑な放熱設計が必要になります。したがって、周波数を選定する際は、サイズ、効率、コスト、放熱のバランスを総合的に考慮する必要があります。

一般的な動作周波数の範囲は20kHz~500kHzで、50kHz~200kHzが最も広く使用される範囲です。これはサイズ縮小と損失制御のバランスを取った結果です。300kHzを超える設計では、従来のシリコンベースのスイッチ素子(MOSFETなど)のクロスオーバ損失が顕著に増加するため、通常、ガリウムナトリウム(GaN)や炭化ケイ素(SiC)などのワイドバンドギャップ半導体スイッチ素子を使用して損失を低減し、高効率を維持します。

単相整流フィルタ回路の計算

整流ブリッジダイオードの耐圧計算:

整流フィルタ後の直流バス電圧は、入力交流電圧のピーク電圧にほぼ等しくなります。交流電圧のピーク電圧は実効値の \\sqrt{2} 倍です。したがって、整流ブリッジダイオードの逆方向耐圧は、最高入力電圧の実効値の \\sqrt{2} 倍以上である必要があります。

また、電源サージや電圧変動に対応するため、通常は余裕係数 $K_{bri}$(一般的に1.5を採用)を加えます。これにより:

したがって、整流ブリッジダイオードの逆方向耐圧は少なくとも562V以上である必要があります。

入力電力:

整流ダイオードの定格電流計算:

整流ブリッジの1個のダイオードに流れる最大入力電流(整流ブリッジは2個のダイオードが交互に導通するため、2で割る必要があります):

同様に、電源サージや電圧変動に対応するため、余裕係数 $K_{bri}$(一般的に1.5)を加えます:

したがって、整流ブリッジの1個のダイオードの定格電流は少なくとも0.747A以上である必要があります。

上記の計算結果に基づき、本設計では定格電圧1000V、定格電流4Aの整流ブリッジ MSB40Mを選定しました。これは上記の計算要件を満たしています。

入力フィルタコンデンサの計算:

フォワード電源の入力コンデンサ選定には経験式があります:

- 220VAC単一電圧入力の場合は、1~2μF/W

- 全電圧範囲(85VAC~265VAC)入力の場合は、2~3μF/W

経験式に基づき、フィルタコンデンサを計算します:

したがって、上記の計算結果に基づき、150μFの電解コンデンサを選定します。

入力フィルタコンデンサの耐圧選定:

通常、入力交流電圧のピーク電圧より高い値を選定します。本設計では V_{busmax} が374.77Vであるため、400Vまたは450Vを選定できます。

フォワード変圧器の計算

余裕を考慮し、最低入力電圧 V_{busms} を110Vとします。

反射電圧(スイッチング素子がオフになった瞬間に、一次巻線が磁気エネルギーの放出によって誘導する電圧)$V_{OR}$ を 100V と定義します。100Vは、広範な入力電圧(110V/220V AC)を想定したフォワード電源設計における典型的な実用値です。

一次側MOSFETのオン時のドレイン・ソース間電圧 V_{ds} を4Vと定義します。

最大デューティ比の計算:(計算しなくても、経験的に0.45を設定しても構いません。フォワード電源のデューティ比は通常0.5以下に抑えられます)

一次側電流のピーク値の計算:

- 入力平均電流:

- ピルピル電流 I_R とピーク電流 I_P のリップル係数 K_{RP} を0.8(CCMモード)と設定し、一次巻線のピーク電流 I_P を計算します:

変圧器磁化インダクタンスの計算:

- フォワード変圧器の磁化インダクタンスの計算式より、一次側の磁化インダクタンス L_P を求めます:

AP値の計算と磁芯の選定:

磁芯面積積(AP)= AW × Ae(磁芯窓面積AWと磁芯有効断面積Aeの積)

- 変圧器窓埋め込み係数 K_o を0.4、電流密度係数 K_j を3.95、磁束密度 B_w を0.2Tとし、必要な最小AP値を計算します:

- 選定する磁芯のAP値は、設計値の2倍以上であることが望ましいです。本設計ではPQ2620磁芯を使用し、磁芯マニュアルによるとAP値は0.7188 \\mathrm{~cm}^{4} です。

なぜ磁束密度 B_w を0.2Tに設定するのか?

1. 磁芯の飽和を回避する

- 磁芯飽和:磁束密度が材料の飽和磁束密度 ( B_{\\text{sat}} ) を超えると、磁芯は導磁能力を失い、インダクタンスが急激に低下し、変圧器が機能しなくなります。

- フェライト磁芯の特性:一般的なスイッチング電源用磁芯(PC40、PC44、PC95など)の B_{\\text{sat}} は100°Cで約0.3~0.4Tです。

- 安全マージン:$ B_w = 0.2 \, \text{T} ( B_{\text{sat}} $ の約50~70%)を設定することで、以下の要因に対する余裕を確保します:

- 高温下での B_{\\text{sat}} の低下(フェライト磁芯の B_{\\text{sat}} は温度上昇とともに低下します)。

- 直流バイアス電流による磁束のシフト。

- 入力電圧変動や負荷瞬変によるピーク電流の増加。

2. 磁芯損失の制御

- 高周波損失:スイッチング電源は高周波(通常>20kHz)で動作するため、磁芯損失(ヒステリシス損失+渦電流損失)は磁束密度に対して指数関数的に増加します。

- 損失最適化:経験的に、 B_w を0.1~0.25Tの範囲に設定すると、磁芯損失と銅損のバランスが良く、全体的な効率が高くなります。0.2Tはこの範囲での一般的な妥協値です。

変圧器一次・二次巻線の巻数計算:

V_F は出力整流ダイオードの順方向電圧降下で、通常0.7Vとします。

- 一次・二次巻線の磁束保存則に基づき、変圧比 N_{PS} を計算します:

- 変圧器の飽和を防ぐため、動作時の最大磁束密度 B_{max} を0.15Tとし、PQ2620磁芯の有効断面積 A_e は119μ($119 \times 10^{-3}\,\text{m}^2$)です。一次巻数 N_P を計算します:

(磁束鎖:$\Psi = N$(巻数)× $B$(磁束密度)× $S$(断面積))

- 変圧器の一次・二次巻数比に基づき、二次巻数 N_S を計算します:

- フォワード変圧器には、制御ICの電源用に補助巻線を追加します。補助巻線の出力電圧 V_{out1} を15Vと設計し、出力電圧と巻数比の関係から、補助電源巻線の巻数 N_{s1} を計算します:

一次・二次巻線の線径と股数の計算:

- 変圧器一次側電流の実効値 I_{prms} を計算します:

- 変圧器二次側巻線の実効電流 I_{\\text{srms}} を計算します:

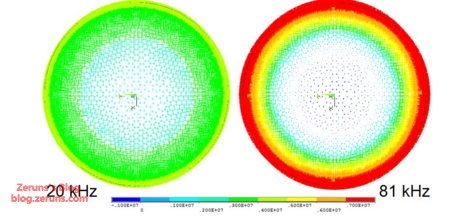

- 変圧器巻線には高周波電流が流れるため、肌効果が発生します。電流は導体内部に均等に流れるのではなく、導体表面近くに集中し、表面に近いほど電流密度が高くなります。導体内部の電流は小さくなります。肌効果により導体の有効利用面積が大幅に減少するため、単一の太い線ではなく、断面積の小さな多芯細線(リッツ線を使用)を用いることで、肌効果を効果的に低減できます。肌深さ $D_m$(最大直径)を計算します:

- 経験的な電流密度は通常 4 \\sim 6 \\,\\text{A/mm}^2 です。一次巻線の使用線径 D_p と股数 P_p を以下のように設定します:

- 一次巻線の電流密度 j_p が4~6の範囲内であることを確認します:

- 二次巻線の使用線径 D_s と股数 P_s を以下のように設定します:

- 二次巻線の電流密度 j_s を計算します:

参考係数の計算:

- すべての巻線の断面積が変圧器窓を占める割合を計算します:

窓埋め込み係数 K_w は通常、0.1~0.3の範囲が適切です。

変圧器製造仕様書

変圧器のパラメータを計算した後、変圧器メーカーに製造仕様書を渡して製造してもらうか、自ら手巻きすることができます。

巻線構造:| ウィンド層 | 出力端子 | ウィンド線仕様 | 匝数 | 疎巻方式 |

| :----: | :------: | :----------------------: | :–: | :------: |

| 第1層 | 1-2 | Φ0.3mm(#28AWG)*3本並列巻 | 10 | 密巻 |

| 第2層 | 5-6 | Φ0.3mm(#28AWG) | 3 | 密巻 |

| 第3層 | 10-12 | Φ0.35mm(#26AWG)*10本並列巻 | 5 | 密巻 |

| 第4層 | 2-3 | Φ0.3mm(#28AWG)*3本並列巻 | 10 | 密巻 |

巻線詳細メモ:

- 図面に示された同名端に従って巻線すること。1/5/10ピンが同名端であり、巻線時は同名端に注意すること。

- 2ピンはサンドイッチ巻きの接続点である。

- 層間にはテープを挿入し、第2層と第3層の端部には2mm以上の仕切り壁を設ける。

- ピンの出入り部分にはチューブを装着する。

- 1ピンに白点を付けて識別し、インダクタンスを156μH(1-3ピン間で測定、@150kHz)に保つ。

- 各層は均一に巻き、1層分足りない場合は均一に疎巻する。

- 8ピンを切断する。

フレームの出力端子、図面の同名端名端説明、巻線構造図は以下の通り:

トランスに関する情報:

| インダクタンス | 1-3ピン:中心柱を研磨して156μH(@150kHz測定)を確保 |

|---|---|

| 磁芯 | PQ2620 (PC95/PC44フェライト) |

| フレーム | PQ2620_6PIN+6PIN 立式フレーム |

| ベースプレート | なし |

| 耐圧試験 | 1ピン-10ピン:1500VAC(周波数:60Hz、時間:60s) |

| 温度等級 | CLASS F |

| 固定方法 | テープ固定(暫定的に接着剤や浸漬処理は行わない) |

| 出線方法 | すべての出入り線にテフロンチューブまたはナイロン絶縁チューブを装着 |

MOSトランジスタの計算と選定

- MOSがオフ状態の際、MOSのドレイン・ソース間には入力電圧と、二次側から一次側に換算された電圧の合計が印加され、入力電圧が最大のとき、このプレート電圧は最大となる:

- MOSがオフになると、実際のトランスには一次側の漏れインダクタンスが存在し、そのエネルギーは二次側に伝送されず、MOSには結晶容量が存在するため、漏れインダクタンスのエネルギーとMOSの結晶容量がLC共振を起こし、MOSに電圧尖峰が発生する。

- 設計では、この尖峰電圧がMOSデバイスを損傷しないよう抑制する必要があり、通常は専用のRCDクランプ回路で尖峰エネルギーを吸収するが、同時にMOSを選定する際には耐圧に十分なマージンを設ける必要がある。本設計では1.5倍の電圧マージンを確保し、$K_{vmos}=1.3$とする。

- よって、選定するMOSの耐圧は以下を満たす必要がある:

- MOSの有効電流は一次側電流の有効値と等しく、上記で算出した$I_{prms}=1.184,\text{A}$である。余裕を考慮し、より大きな定格電流のMOSを選定する。

上記のMOS耐圧最小値と一次側巻線の有効電流$I_{prms}$を踏まえ、本設計ではMOSモデルNJH65R600Sを選定した。定格電圧700V、定格電流8Aで、上記の計算選定要件を満たす。

以下の表を確認し、100℃における定格電流が上記で算出した一次側有効電流を上回ることを確認すること。

定格電圧・電流以外に、MOS選定の主なパラメータは導通抵抗$R_{DS(ON)}$と入力容量$C_{iss}$であり、これらはいずれも小さいほど良い。導通抵抗$R_{DS(ON)}$が小さいほど、MOS導通時の損失が低減される。また、入力容量$C_{iss}$はスイッチング損失とドライブ損失に直接影響し、$C_{iss}$が小さいほどスイッチング応答が速く、スイッチング損失も小さくなり、ドライブ回路に必要な充放電電流も小さくなり、ドライブ損失も低減される。

出力ダイオードおよびコンデンサの計算と選定

出力ダイオードの計算と選定:

- MOSがオンしている間、二次側整流ダイオードは逆方向電圧を受けて遮断され、そのプレート電圧は出力電圧と一次側巻線から二次側に換算された電圧の合計となる。入力電圧が最大のとき、この電圧は最大となり、ダイオード遮断時に受ける電圧は:

-

ダイオードが遮断される際、トランスの二次側巻線に存在する漏れインダクタンスのエネルギーがダイオードの結晶容量とLC共振を起こし、ダイオードのオフ時に尖峰電圧が発生する。設計選定では、一定の耐圧マージンを持つダイオードを選定する必要があり、本設計では1.5倍の電圧マージンを確保し、$K_{vdio} = 1.5$とする。

-

よって、選定するダイオードの耐圧は以下を満たす必要がある:

-

上記で算出したダイオード耐圧最小値と二次側巻線の有効電流$I_{prms}$を踏まえ、本設計ではダイオードモデルSBDD10200CTを選定した。定格電圧200V、定格電流10Aで、上記の計算選定要件を満たす。

-

また、ダイオードはショットキーダイオードを選択する必要がある。ショットキーダイオードは低い順方向電圧降下(Vf) を有し、導通損失を大幅に低減し、電源効率を向上させる。また、逆回復時間が非常に短い(通常<10ns)ため、スイッチングプロセス中のエネルギー損失や電圧振動を抑制でき、高周波フォワード電源に特に適している。

-

ショットキーダイオードの代わりに同期整流ダイオード(同期整流コントローラ+MOSトランジスタを統合)を使用することも可能である。同期整流技術ではMOSトランジスタがダイオードの代わりに使用され、コントローラがMOSのオン・オフを精密に制御する。その利点は導通抵抗($R_{ds(on)}$)が極めて低いことで、導通電圧降下と損失をさらに低減し、効率を向上させる(特に大電流出力時に顕著)。

出力コンデンサの計算と選定:

- MOSがオンし、二次側ダイオードが遮断されると、コンデンサが負荷に電力を供給し、電圧が徐々に低下して出力電圧リップルが発生する。

- コンデンサ電流は負荷電流と等しく、コンデンサ電圧の低下率はコンデンサ電流をコンデンサ容量で割った値となる。

- リップル電圧は、電圧低下率に一次側MOSのオン時間(すなわち二次側ダイオードの遮断時間)を掛けた値である。

- 消費電子機器用スイッチング電源の出力電圧リップル率(リップル電圧のピーク・トゥ・ピーク値を出力電圧で割った百分率)は通常1%~2%以内とされる。本設計では出力電圧24Vであるため、リップル電圧は0.24V~0.48Vの範囲とする。より低いリップル電圧も可能だが、その場合必要な容量は大きくなる。本設計では$\Delta V_{out} = 0.1,\text{V}$と設定し、出力コンデンサ容量は次のように計算される:

- 上記は理想コンデンサ(内部抵抗なし)の計算値である。実際のコンデンサにはESR(等価直列抵抗)が存在し、リップルを増加させる。異なるコンデンサモデルのESRは異なるため、通常は経験的に理論値より大きな容量を選定し、実際の試作で調整する。

- ESRを低減するため、複数のコンデンサを並列接続する。本設計では、220μF/35Vの電解コンデンサを2個並列に使用し、固態コンデンサ(ESRが電解コンデンサより低い)を推奨。さらに、高周波ノイズを除去するために複数のMLCCコンデンサ(例:1μF、100nF)を並列に追加する。

RCD吸収回路の解析と計算

- 回路では2回の振動が発生する可能性がある。第1回は一次側漏れインダクタンス$L_{kp}$とMOSの$C_{oss}$容量によるものであり、第2回は回路エネルギーが消費された後、励磁インダクタンス(一次側インダクタンス)と$C_{oss}$容量によるものである。

-

RCD吸収回路を追加後、MOS両端の電圧がクランプコンデンサ電圧と入力電圧の合計を超えたとき、クランプダイオードが導通し、クランプ回路が動作を開始する。

-

トランスの一次側漏れインダクタンス$L_k$を励磁インダクタンス(一次側インダクタンス)の1%以内に制御するものとする:$L_k=1% \cdot L_p=1.557,\mu\text{H}$(トランス製造後に実際の一次側漏れインダクタンスを測定し、その後の計算には実測値を用いることを推奨。一次側漏れインダクタンスの測定方法:トランスの一次側以外の巻線をすべて短絡し、LCRブリッジで一次側インダクタンスを測定すると、それが一次側漏れインダクタンスとなる。)

-

スイッチング素子の最大電圧$V_{dsmax}$は700Vである。

-

余裕を考慮し、クランプコンデンサ電圧$V_{clamp}$を以下のように設計する:

- 一般的なRCD吸収計算式を用いて、クランプ抵抗$R_c$とクランプコンデンサ$C_c$を計算する:

- クランプ電力を計算すると:

- クランプ抵抗には20kΩ、クランプコンデンサには1nFを使用し、2Wの電力抵抗を選定する。クランプコンデンサの電圧を考慮し、起動初期にクランプコンデンサに高電圧が印加されるため、耐圧1kVのフィルムコンデンサまたは1206パッケージのMLCCを選定する。同様に、クランプダイオードには耐圧1kVのFR107を選定する。

資料ダウンロード

手動計算が面倒な場合は、Mathcad計算書またはSMPSKitソフトウェアを使用して計算できます。ダウンロード先は以下の通り:

- 123クラウド:https://www.123684.com/s/2Y9Djv-A3TdH

- バイドゥクラウド:https://pan.baidu.com/s/1USh47nHgYxjTzTJgo4DVTQ?pwd=xyxf 抽出コード: xyxf

トランス巻き方

私は初めてトランスを巻きました。あまりうまくありませんので、参考程度にお使いください。

すべての巻線は同名端ピンから同じ方向に巻きます!

以下の画像は、エナメル線(左)とリッツ線(右)で巻いたものです。

PQ2620磁芯の直径は14.5mmであり、円周の公式$L = \pi d$より、1回転の長さは45.53mmです。これに匝数を掛けることで各巻線の必要長さが得られ、さらに10~20cmの余裕を加えてエナメル線を切断します。

第1層: まず一次巻線の第1層を巻きます。直径0.3mmのエナメル線3本を並列にし、トランスフレームの1ピンから巻き始め、10回巻きます。(リッツ線は0.1×30を使用しました)

最初の層を巻き終えたら、線を上に巻き上げ、次にテープを1層巻きます(マラテープまたはポリアミドイミドテープを使用)。その後、線を垂直に下に引き、2番ピンに巻き付け、さらに2層テープを巻きます。第2層: 両側にガードウォールを巻き、次に0.3mmのエナメル線を1本だけ5番ピンに巻き、上層の巻き方向に沿って3回巻いて6番ピンに到達させ、最後に2層テープを巻きます。(リッツ線には0.1×10を使用しました。)

第3層: 両側にガードウォールを巻き、次に直径0.35mmのエナメル線10本を並べてトランスフレームの10番ピンに巻き、上層の巻き方向に沿って5回巻いて12番ピンに到達させ、最後に2層テープを巻きます。(リッツ線には0.1×60を使用しました。)

第4層: 初級巻線を継続し、2番ピンから始めて上層の巻き方向に沿って10回巻いて3番ピンに到達させます。巻き終えたら、垂直に下に引き、最後に2層テープを巻きます。

次に、各ピンのエナメル線をピンにはんだ付けします。一部のエナメル線は、はんだ付け前に刃物で表面の塗膜を削る必要があります。リッツ線は、はんだごての高温でしばらく加熱すればそのままはんだ付けできます。

フライバックスイッチング電源では、トランスは1サイクルで伝送するエネルギーを蓄積する必要があります。磁気飽和を防ぐため、通常、磁気コアに気隙を設けてヒステリシスループを変化させ、飽和磁界強度を増加させ、1サイクルあたりの伝送エネルギーを増加させます。気隙の設置方法には、研磨気隙とパッド気隙の2種類があり、パッド気隙の方が簡単です。

最後に磁気コアを閉じ、圧力を加えて初級巻線のインダクタンスを測定します。測定値が目標値(ここでは156μH)より大幅に大きい場合は、ファイルや他の研磨工具で磁気コアの中央円柱(気隙研磨)を少しずつ削り、削るたびに測定を繰り返し、目標値にわずかに超過する程度まで調整します。その後、全体をテープでしっかりと巻き付けます。

あるいは、パッド気隙方式も可能です。磁気コアの両側に数層のテープや薄い紙などを挟み、1層追加するたびにインダクタンスを測定し、目標値にわずかに超過する程度まで調整したら、全体をテープでしっかりと巻き付けます。

パッド気隙は研磨気隙よりも漏れインダクタンスが大きくなります。

完成後、再度測定したところ、このトランスの初級巻線のインダクタンスは158.8μHでした。

初級巻線の漏れインダクタンスを測定するには、他の巻線を短絡し、初級巻線のインダクタンスを測定します。この場合、測定値は2.7μHで、やや大きめでした。

オープンソースプロジェクトのおすすめ

- 三相電力量計をオープンソース化しました。家庭の電力使用状況を簡単に監視できます: https://blog.zeruns.com/archives/771.html

- STM32を用いた同期整流Buck-Boostデジタル電源:オープンソース https://blog.zeruns.com/archives/791.html

- LM25118自動昇降圧可調DCDC電源モジュール:https://blog.zeruns.com/archives/727.html

- CH32V307を用いたスマート電子負荷のオープンソース、組み込みコンテスト作品: https://blog.zeruns.com/archives/785.html

- EG1151大出力同期整流可調昇降圧電源モジュール(TypeC PD高速充電入力対応)オープンソース:https://blog.zeruns.com/archives/794.html

- オープンソース 140W+65W昇降圧PD3.1高速充電モジュール(2C+1Aポート)、205Wデスクトップ充電器:https://blog.zeruns.com/archives/801.html

- オープンソースTypeC拡張ドック、4つの10Gbps USB-Aポート+2.5Gネットワークカード+カードリーダー:https://blog.zeruns.com/archives/868.html

推奨記事

- コスパの良い安価なVPS/クラウドサーバーのおすすめ: https://blog.zeruns.com/archives/383.html

- Minecraftサーバー立ち上げガイド:https://blog.zeruns.com/tag/mc/

- クロスボーダーエコマース独立サイト構築ガイド、WordPress外貿サイト構築:https://blog.zeruns.com/archives/889.html

- ZGRL-80 撮影ライトの分解分析と回路設計:https://blog.zeruns.com/archives/882.html

- 機械革命Code10AIノートPC(Ultra7-255H)の簡単開封レビューと分解:https://blog.zeruns.com/archives/895.html

- GL-RM1PEの簡単開封レビューと分解、一般PCにBMCリモート管理機能を実装:https://blog.zeruns.com/archives/900.html