本文はTIのアプリケーション・ノート文書(ZHCA710 – Jun. 2017)からの転載です

著者:Wiky Liao / Kevin Zhang

PDF文書ダウンロードリンク:https://www.123865.com/s/2Y9Djv-1uTdH

概要

PCBロゴウスキーコイルは応答速度が速く、線形性に優れ、コストが低いといった特徴を持つため、交流大電流の場面で広く応用されています。例えば、交流モータ制御、エスカレーター、架空線やケーブルなどです。ロゴウスキーコイルの出力信号は元の電流の微分であるため、積分回路を組み合わせて設計する必要があります。本稿では、PCBロゴウスキーコイルの動作原理と設計上のポイントを詳細に説明し、TIのオペアンプOPA2333を用いた高性能積分回路の設計により、お客様がアプリケーションの要件に合ったPCBロゴウスキーコイル電流検出ソリューションを迅速に設計できるよう支援します。

1 ロゴウスキーコイル

1.1 ロゴスキーコイルの概要

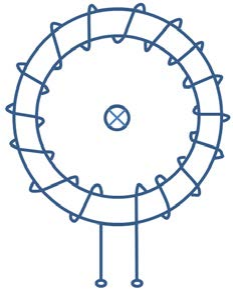

ロゴスキーコイルは非接触型電流センサであり、主にフレキシブル型とハード型の2種類に分類されます。PCBロゴスキーコイルはハード型に属します。その構造の特徴は、導線が非磁性の環状コアに均等に巻かれて環状コイルを形成し、被測定電流がコイル中心を通過することです。Figure 1に示します。

Figure 1 左図はロゴスキーコイル構造概略図、右図はPCBロゴスキーコイルレイアウト

1.2 ロゴスキーコイルの動作原理

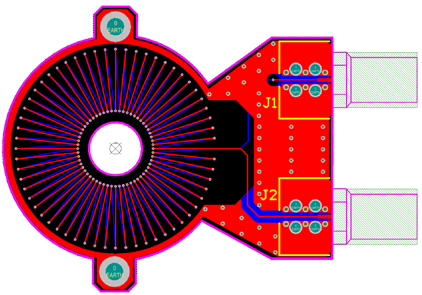

無限長の通電導線がロゴスキーコイル中心に垂直に通過すると仮定し、導線電流をIとします。コイルの内径をa、外径をb、板厚をh、PCB導線の透磁率をμとします。Figure 2に示します。

Figure 2 ロゴスキーコイル解析モデル、左図は上面図、右図は断面図

ビオ・サバールの法則により、x位置の磁束密度:

トップ層導線とボトム層導線はビアで接続され、1ターンを構成します。各ターンが発生する磁束:

レンツの法則により、Nターンコイルが誘起する電圧:

式(3)において、Mは相互インダクタンス係数です。

式(3)により、ロゴスキーコイルの出力は電圧であり、測定電流とは微分関係にあることが分かります。そのため、ロゴスキーコイルは交流電流測定用途のみに適用され、使用時にはインテグレータを併用する必要があります。

1.3 PCBロゴスキーコイルの設計ポイント

1.3.1 ターン数の制限

ロゴスキーコイルの主要パラメータは相互インダクタンス係数Mであり、その値は主にターン数、板厚、コイルの内径および外径に依存します。ただし、PCBのビアサイズと製造技術レベルの制限により、実際のターン数は無限大にはできず、一定の制限があります。ターン数計算モデルをFigure 3に示します。

ビアV1とV2間の距離:

製造技術レベルの制限により、これらの隣接ビア間の距離は少なくともパッドとビアの直径差の3倍以上である必要があります。つまり:

ここで$V_p$はビアのパッド直径、$V_h$はビア径です。

式(4)と(5)により、2つの接続ビアの角度が求まります:

したがって、PCBロゴスキーコイルの最大ターン数は:

一般的に、板厚も最小ビアサイズを決定するため、コイルを設計する前にPCB製造メーカーに確認することをお勧めします。

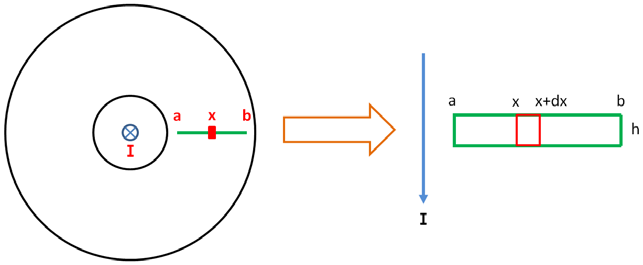

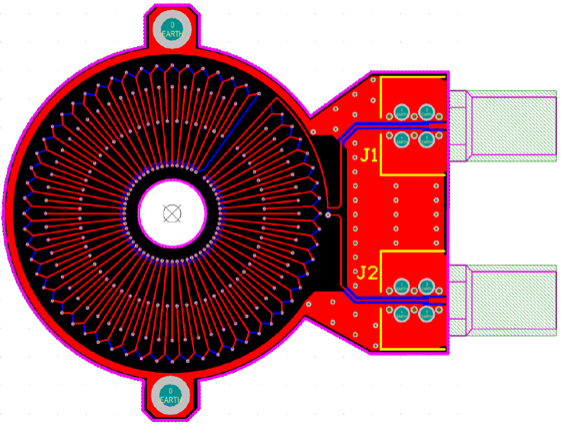

1.3.2 スペースの有効活用

PCBロゴスキーコイルは一般的に放射状配線となり、外側のターン間に大きな空隙が生じます。そのため、大きなターン間に小さなターンを追加できます。これにより、板サイズを変えずにコイルの相互インダクタンス係数を増大させることができます。Figure 4に示します。小さなターンの内径を$c$、外径を$d$とすると、コイルの相互インダクタンス係数は:

Figure 4 小さなターンを追加したロゴスキーコイル

板サイズが固定されている場合、非常に大きな相互インダクタンス係数が必要な場合は、複数のPCBロゴスキーコイルを直列接続することを検討できます。つまり、Figure 4のJ2出力を次のPCBコイルのJ1に接続し、信号の重ね合わせを実現します。

2 積分回路設計

2.1 理想積分回路の不足と改善

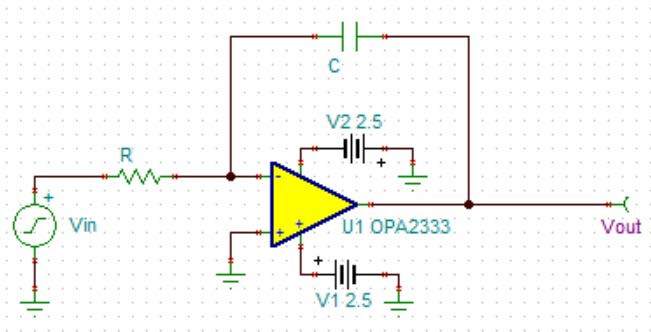

ロゴスキーコイルの出力電圧は測定電流信号の微分であるため、後段に積分回路がない場合、電流に僅かな高周波成分が含まれるだけで、コイル出力端に高電圧が誘起され、基本波信号が埋もれてしまいます。そのため、後段には積分回路が必要で、信号を復元します。理想積分回路をFigure 5に示します。

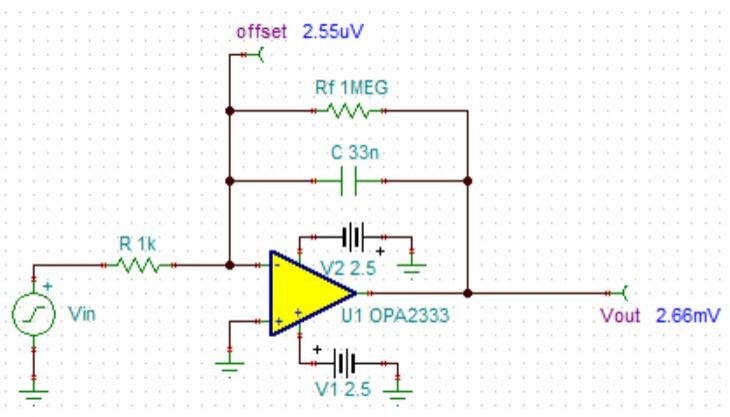

Figure 5 左図は理想積分回路の原理図、右図は積分出力電圧波形

入力信号のオフセットがゼロの場合、積分後の波形オフセットもゼロであるべきです。しかし、上図により、積分出力電圧のオフセットはゼロではなく、波形は電源レールにドリフトしていることが分かります。実際のオペアンプでは状況はより悪化し、波形は電源レールでクリッピングが発生し、飽和歪みまたはカットオフ歪みを引き起こします。その主な原因は、現在使用されているオペアンプは理想オペアンプではなく、固有のオフセット電圧を持っていることです。他の回路がないため、オフセットは積分コンデンサを充電し、長時間では必然的にコンデンサ飽和を引き起こし、クリッピングを発生させます。そのため、積分コンデンサの両端に抵抗を並列接続し、コンデンサに放電回路を提供して回路を安定動作させる必要があります。Figure 6に示します。抵抗を並列接続した後、回路の積分性能を分析する必要があります。

Figure 6 積分回路並列抵抗後の性能分析

オペアンプの反転入力端子において、キルヒホッフの電流方程式を建立します:

式(9)は1次非斉次方程式であり、これを解くと:

ここで$C_1$は定数です。入力信号$V_{in} = \cos(\omega t)$と仮定すると、式(10)は簡略化されます:

周波数領域から、並列抵抗後の回路の増幅率は:

式(11)と(12)は2つの重要な情報を伝えています:

- 時間$t$が徐々に大きくなると、出力端電圧$V_{out}$の指数部分$C_1 e^{-\frac{t}{R_f C}}$は徐々に小さくなり、最終的には完全に無視できるようになります;

- $R_f \gg \frac{1}{\omega C}の場合、\varphi \approx 0^\circ$となり、増幅率は理想の$\frac{1}{\omega RC}$に近づきます。このとき、出力端電圧は入力信号の反転積分であると見なすことができます。

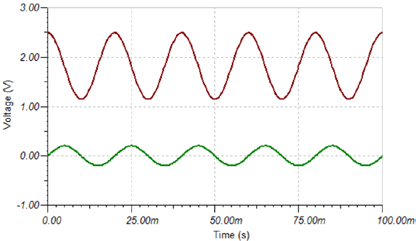

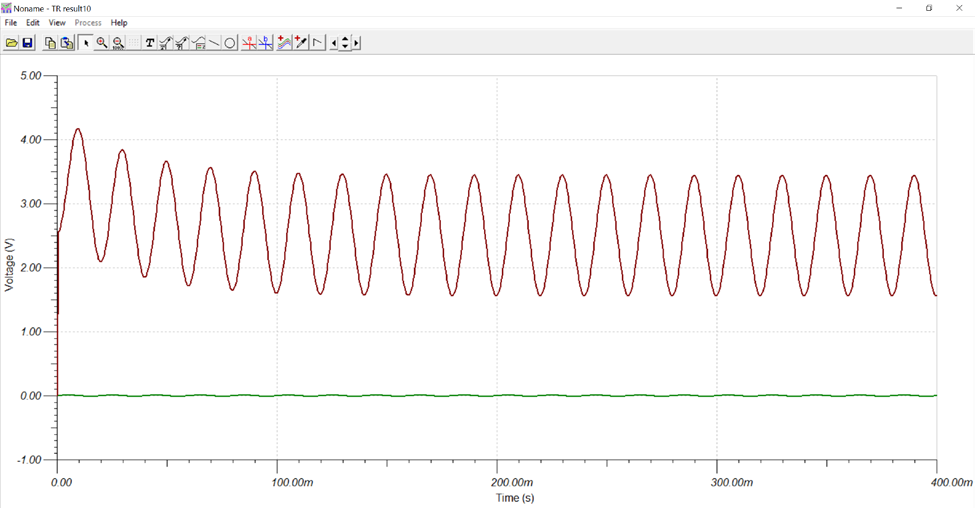

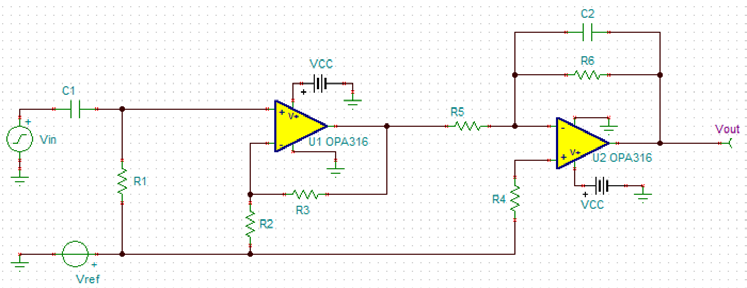

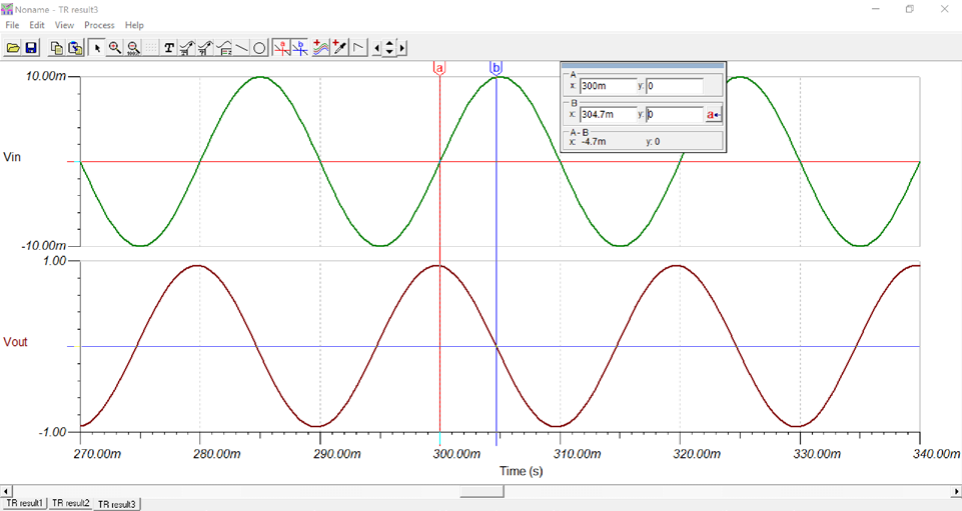

以上の分析に基づき、積分回路のシミュレーション結果をFigure 7に示します。緑色の曲線が入力、赤色の曲線が出力です。出力信号は初期段階で指数因子の影響を受けて変動が見られますが、最終的に安定し、積分効果は非常に良好です。

Figure 7 並列抵抗後の積分回路シミュレーション波形

2.2 積分回路のオペアンプ選定

良好な積分効果を得るためには、一般的に帰還抵抗Rfをできるだけ大きく選定する必要がありますが、大きければ良いというわけではありません。その主な原因は、積分回路がオペアンプのオフセットにとって同相増幅回路となるため、帰還抵抗Rfが大きすぎると出力端に大きな直流オフセットが発生し、積分ドリフトの抑制能力が弱まることです。そのため、積分回路内のオペアンプは非常に小さなオフセット値を持つ必要があり、出力端の直流レベルをできるだけ低く抑える必要があります。OPAx333はTIがゼロドリフト機能を持つ低オフセットオペアンプとして発売した製品で、内部でデジタルキャリブレーションを採用することでオフセットおよびドリフト電圧を大幅に低減しています。そのオフセット最大値はわずか10μVで、0.05μV/°Cという低ドリフトも実現しており、積分回路設計に最適です。Figure 8ではOPA2333積分回路の直流シミュレーションを行っており、帰還抵抗が積分抵抗の1000倍という条件下でも出力は2.66mVのみと、性能が非常に優れています。同時にOPAx333の最大静止電流は25μAのみであり、低消費電力・高性能な演算増幅器です。

Figure 8 OPA2333 積分回路直流シミュレーション

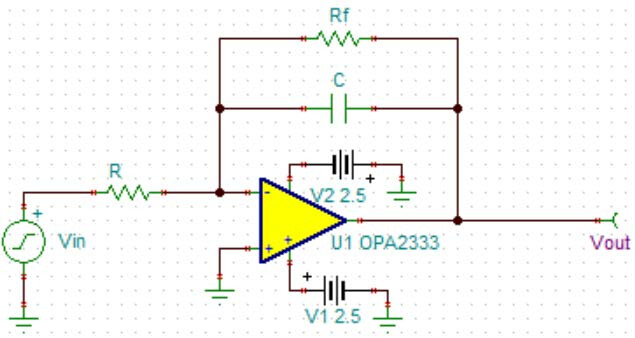

2.3 単電源積分回路設計

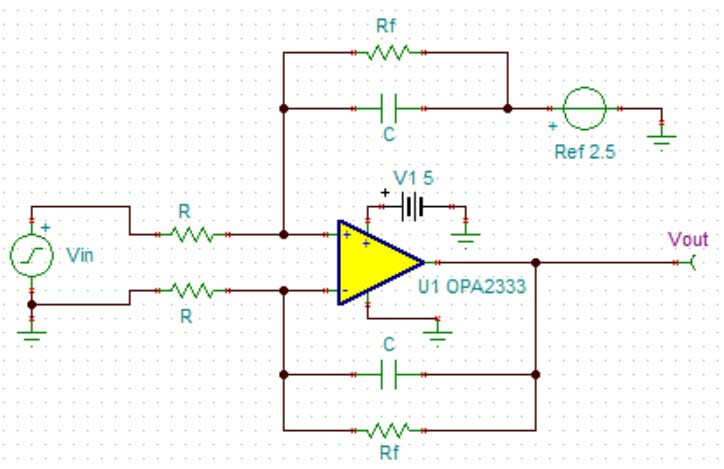

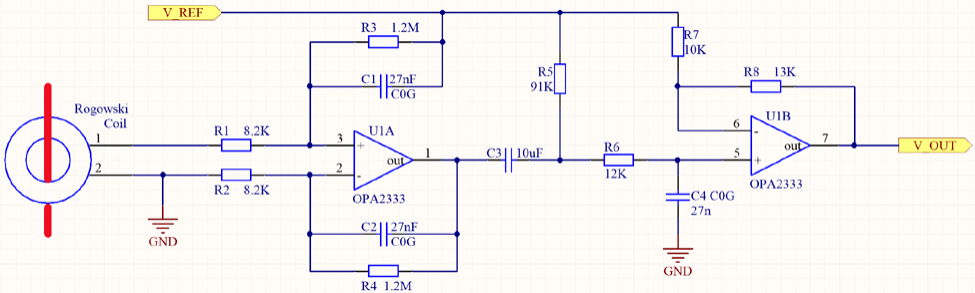

前述の積分回路はデュアル電源積分方式を採用していましたが、多くの顧客アプリケーションでは単電源駆動のみがサポートされているため、単電源積分回路を設計する必要があります。差動オペアンプの回路構造を参考に、Figure 9のような単電源積分回路を設計しました。

Figure 9 単電源積分回路

前述の分析方法と同様に、入力電圧$V_{in} = \cos(\omega t)$と仮定すると、出力電圧は:

式(13)の核心解釈:

- 出力特性:出力電圧は入力信号の同相積分であり、直流オフセット$V_{ref}$を含みます;

- シミュレーション検証:シミュレーション出力波形はFigure 10に対応しており、緑色の曲線が入力信号、赤色の曲線が出力信号で、システムの積分性能は良好に表現されています。

Figure 10 単電源積分回路シミュレーション波形

2.4 高性能積分回路の注意事項

2.4.1 オフセット補正

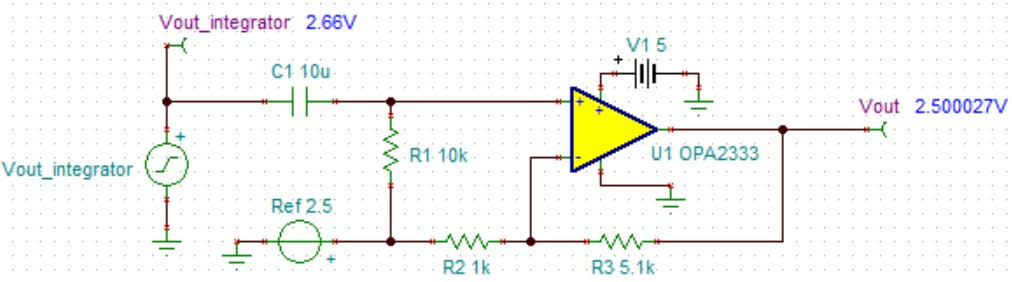

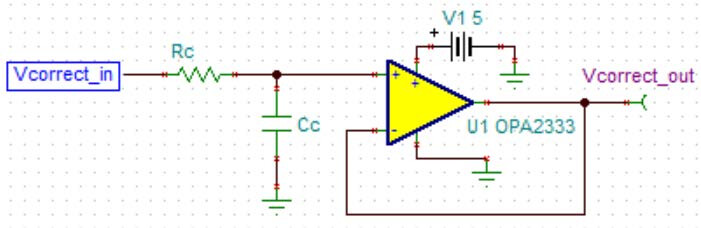

前述の回路分析により、出力端電圧のオフセットには一定の誤差が存在することが分かります。OPAx333オペアンプの場合、最大でも数mV程度です(性能の劣るオペアンプでは数百mVに達する可能性があります)。出力端のオフセット要求が高い場合は、オフセットを再補正する必要があります。補正回路は積分回路の後段に配置され、Figure 11に示します。シミュレーション結果により、出力端Voutの直流オフセットとプリセットされたRef値との差は27μVのみであり、オフセット効果は非常に優れています。同時に非反転増幅抵抗R2およびR3は信号をさらに調整でき、出力をフルスケールに達成できます。

Figure 11 オフセット補正回路およびDCシミュレーション結果

2.4.2 高周波故障成分の測定

一部のアプリケーション(AFCIなど)では、ユーザーは主に電流の高周波故障成分に関心があり、故障状態で適切な動作(回路遮断など)を行う必要があります。このような場合、低周波帯域の正常動作電流はそれほど重要ではなく、無視することもできます。このアプリケーションに対しては、まずハイパスフィルタを設定して低周波成分を除去します。その後、増幅回路を追加して高周波成分の信号を増幅し、積分後の信号を十分に監視できるようにします。応用回路をFigure 12に示します。

Figure 12 高周波故障成分測定回路

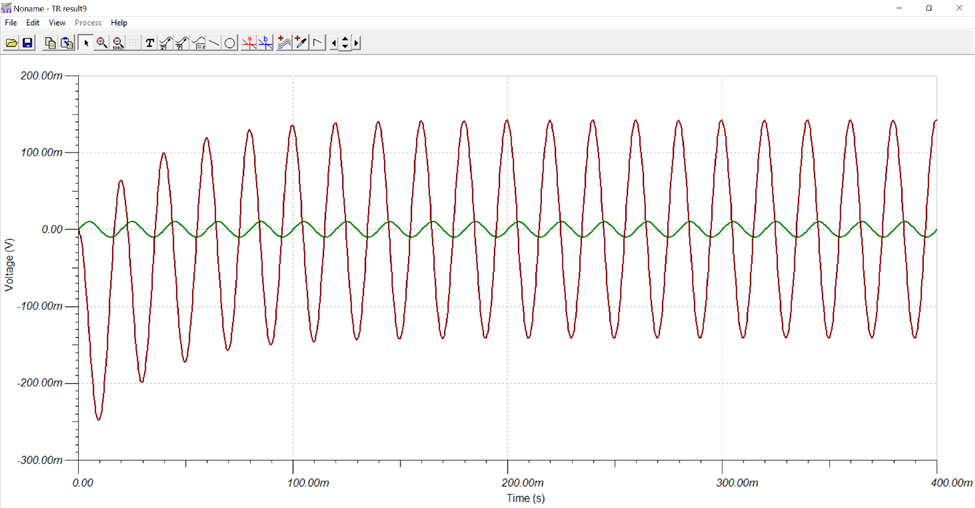

2.4.3 低周波位相補正

前述の分析により、積分回路には一定の位相角誤差が存在し、周波数が低いほど位相角誤差が大きくなります。Figure 8の回路を例に、50Hzの動作周波数でのシミュレーション波形結果をFigure 13に示します。緑色の曲線が入力、赤色の曲線が積分出力です。

Figure 13 反転積分回路シミュレーション波形位相分析

理論的には、50Hzの正弦波信号を反転積分すると、積分後の波形のゼロクロス点は入力信号より90°遅れ、時域ではb点がa点より5ms遅れる効果が表れます。しかし、Figure 13により、a点とb点の時間差は4.7msであり、位相角に換算すると約84.6°です。つまり、積分出力波形は設計予想より約5.4°位相角進んでいます。一般的に、位相補正問題を重点的に考慮すべき場面は2つあります。1つはシステムの位相要求が高い場合(遮断器の開閉制御など)で、位相精度不良が大きなアークを発生させ、設備および人身安全を脅かします。もう1つはシステム自体の動作周波数が低い場合(電力企業にとっては商用周波数(50/60 Hz)が主要な応用場面)で、低周波が大きな位相角誤差をもたらすことです。

以下、位相角誤差の発生メカニズムと補正措置を分析します。積分回路の位相角誤差:

オフセット補正回路を採用した場合、別の位相角誤差も発生します:

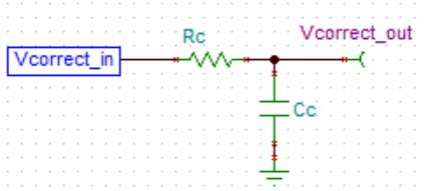

$\varphi_1$と$\varphi_2$はどちらも進み位相角を発生させるため、打ち消すための遅れ補正回路が必要です。Figure 14に示します。位相補正は主にアクティブとパッシブの2種類に分類されます。アクティブ補正は最も効果的で、負荷インピーダンスの影響を受けませんが、追加のオペアンプが必要でコストが高くなります。パッシブ補正はコストが非常に低いですが、補正効果は負荷インピーダンスの影響を受けます。一般的に、応用要求に応じてどの方式を採用するかを決定します。良好な補正効果を確保するため、積分回路および低周波補正回路のコンデンサはできるだけC0GまたはNP0シリーズを選定してください。

Figure 14 左図はアクティブ位相補正、右図はパッシブ位相補正

3 システムテスト

3.1 性能テスト

商用周波数50Hz応用場面を例に、Figure 15のような単電源積分回路を設計しました。設計目標は、出力端電圧が入力電流と線形変化し、比例係数が52.4となることです。ロゴスキーコイルの設計パラメータは101nHです。

Figure 15 商用周波数応用場面の単電源積分回路原理図

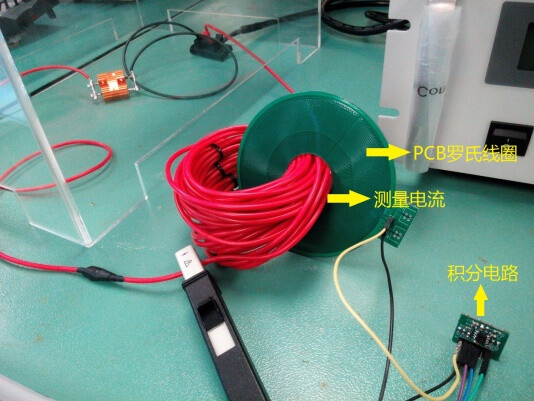

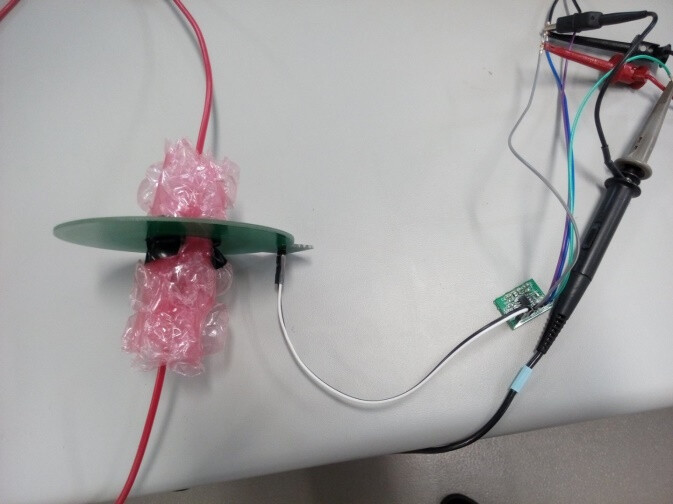

電流導線をPCBロゴスキーコイルに垂直に通します。測定機器の出力電流が小さいため、ターン数を増加させ、測定環境および波形をFigure 16に示します。

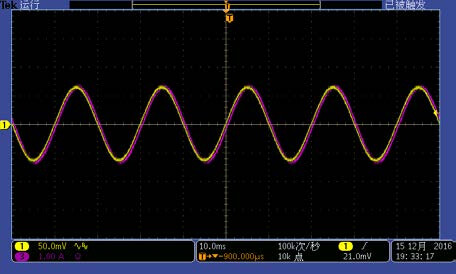

Figure 16 左図は測定環境、右図は測定波形(紫色部分が電流、黄色部分が積分出力電圧)

Figure 16右図により、出力端電圧の波形は電流波形と基本的に一致しており、良好な測定効果が得られました。測定データをTable 1に整理します。

Table 1 PCBロゴスキーコイル測定データ

| 入力電流(RMS)/A | 出力電圧(RMS)/mV | 入力電流(RMS)/A | 出力電圧(RMS)/mV |

|---|---|---|---|

| 0.46 | 20.95 | 2.74 | 124.8 |

| 0.92 | 42.03 | 3.26 | 148.0 |

| 1.39 | 63.02 | 3.68 | 166.8 |

| 1.83 | 83.70 | 4.01 | 185.4 |

| 2.30 | 104.6 | 4.46 | 202.5 |

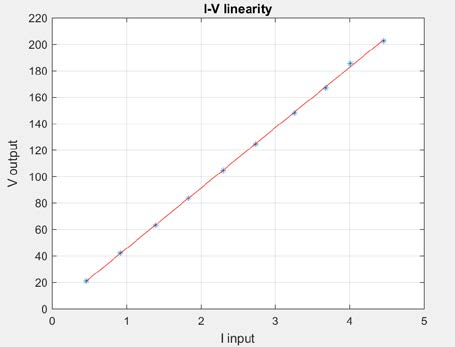

Table 1のデータに対して線形近似を行い、Figure 17に示します。結果により、出力電圧と入力電流の線形性は非常に良好であり、以下の関係式をほぼ満たします:

Figure 17 出力電圧と入力電流の線形近似

理論計算により、出力電圧と入力電流の関係式は:

係数の測定結果45.64は理論結果47.21よりやや小さいですが、誤差は5%以内に制御されており、基本的に設計目標に符合しています。

3.2 性能テストの誤差分析と改善測定誤差は主に通電導線とコイルの相対位置に関係しています。誤差を小さくするため、一般的には長い通電導線をロゴスキーコイルの中心に垂直に通し、できるだけ線の曲げを減らすことが求められます。今回のテストでは測定電流が小さいという制限がありましたので、コイルの等価相互インダクタンス係数を高めるために巻き数を増やす方法を採用しました。そのため、通電導線がコイルの中心をすべて通過せず、かつ大きなケーブルの曲げが存在しました。その結果、実測されたコイルの相互インダクタンス係数は理論値よりも小さくなりましたが、差は大きくなく、設計目標と基本的に一致しています。

3.3 妨害テスト

ロゴスキーコイルで電流を測定する際、被測定電流はコイルの中心穴を通過する必要があります。しかし実際の作業環境では、被測定電流の周囲には通常他の交番電流が存在します(三相交流電送電の場合など)。ロゴスキーコイルの工作原理によると、周辺の交番電流もコイル内に交番磁場を発生させ、被測定電流を妨害します。したがって、ロゴスキーコイルの周辺電流に対する妨害抑制能力を分析することが必要となります。

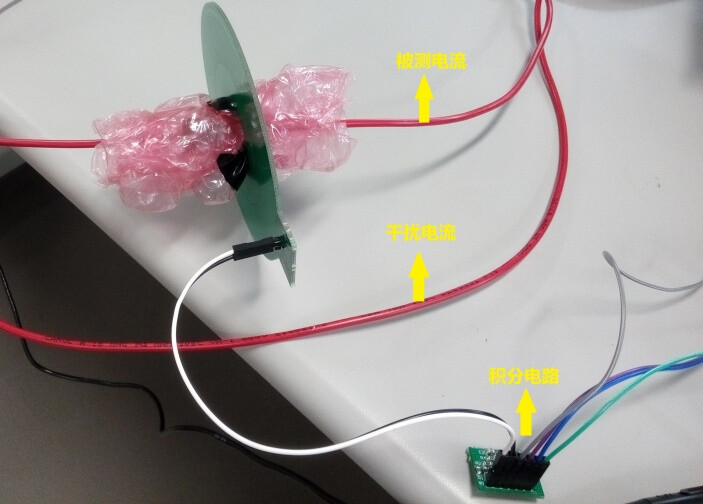

妨害テストの基本プロセスは、まず妨害電流がない状態で出力電圧と被測定電流との対応関係を測定します。次に、被測定電流の周囲(つまりコイル外)に妨害電流を追加し、同じ被測定電流における積分出力電圧が変化するかどうかを検証します。この想定に基づき、ロゴスキーコイル妨害テストの測定環境をFigure18に示します。

Figure 18 左図は無妨害電流測定環境、右図は有妨害電流測定環境

測定現場で大きな妨害電流を提供できないという制限があり、より良い妨害効果を得るために、被測定電流の巻き数を増やさず、妨害電流を被測定電流と同程度の大きさにしました。巻き数の補償として、妨害テストでは積分回路の増幅率を大きくしました(Figure15のR7を100Ωに変更)。補足しますが、増幅率が大きすぎると、出力端のオフセットが大きくなる、増幅率の実際のゲインと設計値の偏差が大きくなるなどの欠点があります。そのため、実際の応用では大きな増幅率を選ぶべきではありません。しかし、この妨害抑制テストでは、回路が固定された状況下での妨害信号の被測定信号への影響をより重視しているため、大きなゲインがもたらす影響は大きくありません。

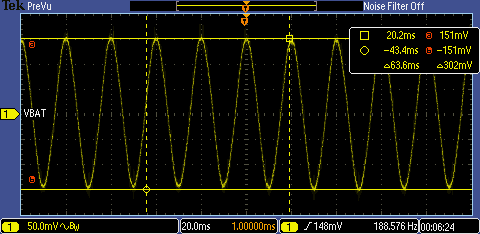

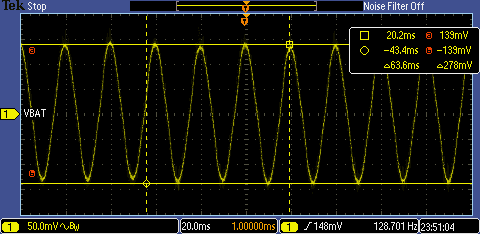

妨害電流の有無において測定された積分出力電圧波形をFigure19に示します。

Figure 19 左図は無妨害電流時の出力電圧波形、右図は有妨害電流時の出力電圧波形

テストデータをさらに整理してTable2に示します。

Table 2 妨害テストデータ

| 被測定電流(RMS)/A | 妨害電流(RMS)/A | 無妨害電流時出力電圧(RMS)/mV | 無妨害電流時出力電圧(RMS)/mV | 誤差% |

|---|---|---|---|---|

| 0.41 | 0.41 | 21.9 | 20.6 | -5.9% |

| 0.82 | 0.81 | 43.1 | 38.9 | -9.7% |

| 1.23 | 1.22 | 65.1 | 58.5 | -10.1% |

| 1.64 | 1.63 | 83.4 | 78.5 | -5.9% |

| 2.06 | 2.04 | 106.1 | 98.3 | -7.4% |

Table2から、妨害電流の導入により出力電圧の振幅が減少し、測定誤差が生じることがわかります。今回のテストでは、誤差は10%程度でした。

3.4 妨害テスト誤差分析と改善

ロゴスキーコイル外に妨害電流が存在する場合、妨害電流の変化により交番磁場が発生し、交番磁場がロゴスキーコイル内に誘起電圧を発生させます。これが測定誤差が存在する根本的な原因です。測定誤差の大きさは妨害電流値に関係し、また妨害電流と被測定電流との距離にも関係します。今回のテストでは、妨害信号が非常に大きく、被測定信号と同程度の大きさであり、かつ妨害信号とロゴスキーコイルとの距離が短かったため、大きな測定誤差が生じました。実際の測定では、妨害電流をロゴスキーコイルから遠ざけるように注意し、条件が許す場合は妨害電流を小さくすることで、測定誤差を小さくすることができます。

4 参考文献

- TI-Design-01063, High Accuracy AC Current Measurement Reference Design Using PCB Rogowski Coil Sensor, Texas Instruments Inc.

- OPA2333 datasheet 2016, Texas Instruments Inc.