ABC

3

少见有提问这么详细的,思路清晰,有图,疑惑点清晰明了,标准的提问啊!

最怕那种自己问题都描述不清的,还要不断追问他才搞懂他到底问什么

4 个赞

知夏

4

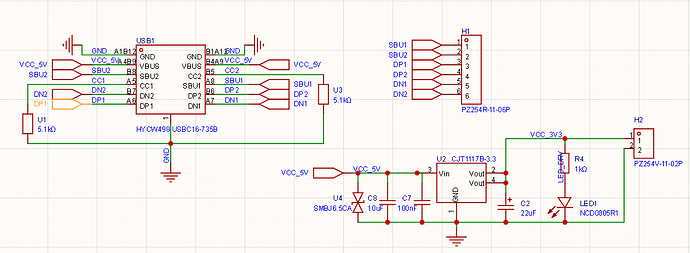

你好!作为新手,你的这份原理图画得非常棒!整体逻辑清晰,Type-C 的 CC 引脚下拉(U1, U3 各 5.1kΩ)做对了,LDO 输入输出电容配置齐全,甚至还考虑到了 TVS 保护,这已经超越了很多初学者的水平。

针对你的疑惑点,我来逐一为你解答,并提供一些工程实践上的建议:

1. Type-C 接线看着乱,画图规范吗?

你目前的画法在电气连接上是完全正确的,但从原理图的“可读性”和“美观度”来说,确实可以优化。

- 改进建议:在实际工程中,为了避免线缆交叉导致视觉混乱,我们通常会使用网络标签(Net Label)。你可以把 USB 接口出来的线拉出一小段后打上网络标签(比如命名为

DP1、DN1),然后在排针 H1 那边也拉出一小段打上同名的网络标签。这样软件会自动将它们连接起来,图面会清爽很多。

2. 排针引出信号线的顺序问题

从纯导电的角度来说,随便排没问题。但考虑到信号完整性和后续使用的便利性,建议遵循以下原则:

- 关键遗漏:缺少 GND! 你的 H1 排针只有信号线没有地线。任何信号都需要回流路径,如果不引出 GND,你用杜邦线把这些信号接到其他板子上时,很容易因为地电位不一致导致通信失败甚至烧毁设备。务必在 H1 中增加至少一个 GND 引脚。

- 信号合并与排序:对于标准的 USB 2.0 通信,Type-C 插座内部为了支持正反插,有两对 D+/D-。通常我们在靠近接口的地方,会把 DP1 和 DP2 短接,DN1 和 DN2 短接。这样你只需要引出一对 D+ 和 D- 即可。

- 排列顺序建议:GND, SBU1, SBU2, DP, DN。把差分信号(DP和DN)挨着放,方便后续接线。

3. TVS 选型 (SMBJ6.5CA) 合适吗?

选型非常稳妥,完全符合需求,但可以稍微优化。

- 参数分析:USB VBUS 正常工作电压是 5V。SMBJ6.5CA 的反向工作电压(Vrwm)是 6.5V,既不会在正常 5V 时误导通漏电,又能有效钳位过压尖峰,参数选得很精准。

- 优化建议:

- 后缀

CA 代表双向 TVS。对于直流电源线(VCC_5V),其实使用单向 TVS(后缀为 A,如 SMBJ6.5A)更好,因为单向 TVS 对负向电压尖峰的钳位效果更佳。

- 封装体积:

SMB 封装对于一个简单的 LDO 降压板来说有点偏大了。如果你追求板子小巧,可以换成 SMAJ6.5A(SMA封装),或者更小的 SOD-323 封装的 ESD 保护管。当然,如果你手头正好有 SMBJ6.5CA,直接用毫无问题。

4. 钽电容的替代方案 (1117 芯片的“坑”)

你在这里提到了一个非常专业且核心的问题!1117 系列芯片对输出电容的 ESR(等效串联电阻)是有严格要求的。

- 1117 是较老的双极型 LDO 架构,它依赖输出电容带有一定的 ESR(通常要求在 0.1Ω 到 10Ω 之间)来保证内部环路的稳定。

- 如果只用 MLCC(陶瓷电容):MLCC 的 ESR 极低(通常只有几毫欧),这会导致 1117 芯片震荡,输出的不是平稳的 3.3V 直流电,而是带有高频纹波的波形。

- 替代方案推荐:

- 方案 A(最推荐,性价比最高):100nF MLCC并联 + 10uF (或22uF) 铝电解电容。铝电解电容天生自带适量的 ESR,刚好满足 1117 的防震荡需求;同时并联一颗 100nF 的 MLCC 用来滤除高频噪声。这是工程中最常见、最廉价的做法。

- 方案 B(体积小):22uF MLCC 串联一个小电阻(如 0.5Ω 或 1Ω)。用电阻人为模拟出 ESR。虽然可行,但增加了物料种类,不如方案 A 简单。

- 总结:你目前使用钽电容是完全没问题的(钽电容的 ESR 刚刚好),但钽电容价格贵且过压容易起火。建议替换为 MLCC + 铝电解电容 的组合。

最后补充一个小细节:

LED 指示灯的限流电阻 R4 (1kΩ)。(3.3V - LED压降约2V) / 1kΩ ≈ 1.3mA。这个电流对于普通的贴片 LED 来说可能会有一点点暗。如果你希望它亮一点,可以把 R4 改成 470Ω 或 510Ω(电流约 2.5mA - 3mA)。

3 个赞

CCC

5

这是一个非常扎实的LDO降压电路的首次尝试!你已经成功掌握了核心概念:通过CC电阻从Type-C接口协商5V电压、添加输入保护和滤波,并提供了输出指示灯。从电气角度看,该电路确实可以成功输出3.3V。

以下是对你提出的问题的详细解答,以及一些专家建议,帮助你进一步提升原理图设计水平。

1. 原理图绘制与Type-C接线标准

你的原理图完全可读,但有一些标准规范可以让你的设计更整洁、更专业:

- 元件标号(Designators):你使用了

U1 和 U3 来表示两个5.1kΩ的CC电阻。根据原理图设计规范,U 通常保留给集成电路使用(例如你的1117稳压器和TVS二极管)。电阻应始终使用 R 作为前缀(如 R1、R2)。

- 网络标签 vs 连线:在简单电路中直接画出绿色连线是可以接受的,但如果线路交叉过多(比如你的DP/DN和SBU信号线),会显得杂乱。在专业设计中,我们通常使用网络标签(Net Labels)——将一段导线命名为“DP1”,另一端也命名为“DP1”,即可实现隐式连接,无需跨页布线。

- 视觉流向:标准做法是输入放在左侧,主处理/电源转换部分居中,输出放在右侧。你基本遵循了这一原则,做得很好!

2. 信号排针(H1)引脚顺序

如果你只是把这些信号引出到排针用于跳线连接,物理顺序并不严格重要。但如果你计划将来用于数据传输,则有一些最佳实践需要考虑:

- 差分对成组排列:USB 2.0依赖于差分信号对(

DP 和 DN),它们应紧挨着放置。更好的引脚顺序为:DP1, DN1, DP2, DN2, SBU1, SBU2。

- Type-C的“翻转”陷阱:Type-C接口支持正反插。当线缆正向插入时,数据走

DP1/DN1;翻转后则走 DP2/DN2。如果你想让这个接口无论线缆方向如何都能正常传输USB 2.0数据,建议在连接器处就将 DP1 与 DP2 短接,DN1 与 DN2 短接,然后只引出一对信号(DP/DN)到你的排针上。

3. TVS二极管选型(SMBJ6.5CA)

你选择的SMBJ6.5CA是安全且可用的,但在性能上略有优化空间:

- 电压等级:“6.5”代表其截止电压为6.5V。这对5V USB线路来说非常合适——正常工作时不会误触发,同时能在电压尖峰达到1117的绝对最大额定值(15V)之前及时钳位。

- 方向性(CA vs A):“CA”后缀表示这是双向TVS。而你的USB VBUS是一个严格的正直流电源,因此实际上更推荐使用单向TVS(SMBJ6.5A)。单向TVS对负电压瞬变更有效(可将其钳位在约-0.7V的安全水平),而双向TVS在负向过冲时可能允许电压降至约-11V才开始动作。

4. 输出电容与“1117 ESR陷阱”

你无意中触及了PCB设计中最著名的难题之一:1117 LDO的稳定性要求。

像1117这类较老的LDO架构必须在其输出端电容上具有特定范围的等效串联电阻(ESR),通常在0.3Ω至22Ω之间,以维持控制环路稳定。

- 你当前的选择(钽电容):钽电容天然具备合适的ESR范围,这正是为什么它长期以来被视为1117的经典搭配。

- 替代方案1:MLCC + 小电阻:这是一个优秀且常见的替代方法!纯陶瓷电容(MLCC)的ESR几乎为零,会导致1117产生振荡,输出噪声大且不稳定。如果你希望使用便宜的10μF或22μF MLCC,只需串联一个0.5Ω至1Ω的小电阻,就能完美模拟钽电容的行为。

- 替代方案2:MLCC + 铝电解电容:这也可行。铝电解提供必要的ESR,而MLCC负责抑制高频噪声。

专业建议:如果你想彻底避免ESR带来的麻烦,最简单的办法是将1117更换为现代的“陶瓷电容稳定型”LDO(例如AP2112或RT9013)。这些新型稳压器专为配合标准MLCC电容设计,无需额外电阻即可稳定工作。

1 个赞

如果对电流要求不高LDO可以选XC6206P332

2 个赞

欸,原来四个引脚才能合成一对差分线嘛,原本还以为两个引脚一对呢  是我学艺不精了

是我学艺不精了

是TypeC接口才这样,因为TypeC允许正反插,上下触点都是相同的引脚,所以引出来要连一起

1 个赞

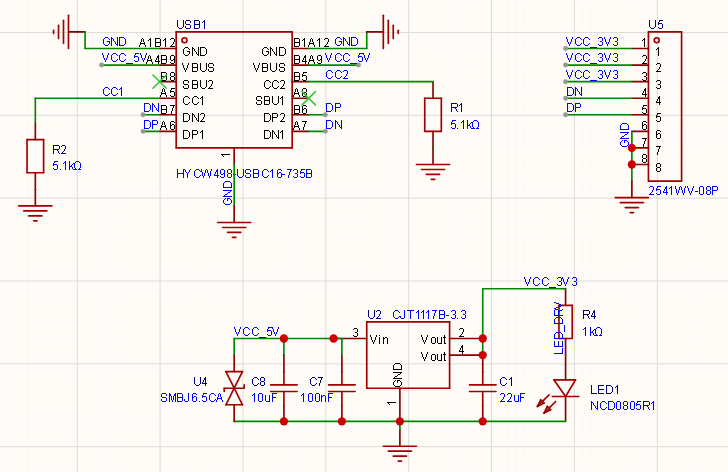

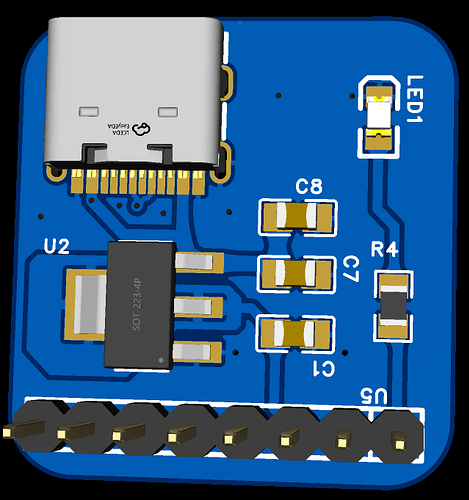

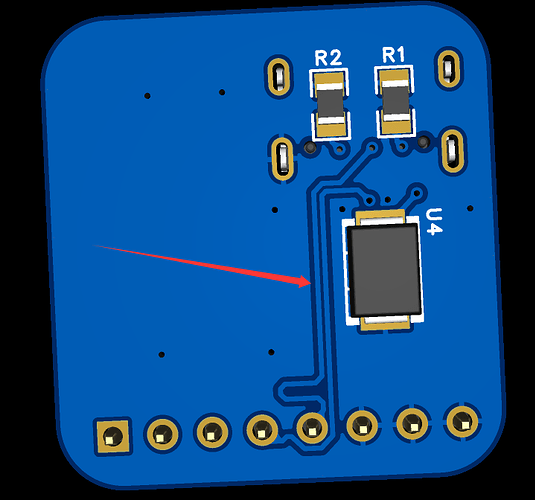

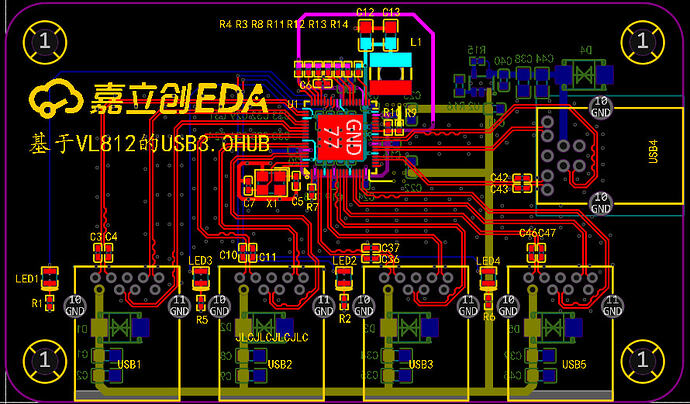

我按照建议调整了原理图,您第二点意思我不知道有没有理解错,能帮我看看嘛?另外我还画了PCB,感觉差分线可能有点没有做好

zeruns

11

- TVS放靠近接口处,走线需先经过TVS再到其他器件,不然就不起作用了

- DP和DN数据线最好也加个ESD管,不过其实现在大部分芯片都内置有ESD了

- USB走线还需要做90Ω阻抗匹配,还要做等长(其实低速不做也没啥问题)

- 你可以到立创开源平台多看看别人的作品学习一下

- 电源网络可以直接用自定义铺铜过去

- TVS可以换个封装小一点的型号

可以看看立创这篇文档,有讲USB接口应该怎么走线,也有图:https://wiki.lceda.cn/zh-hans/design-production/pcb-design/moduler-design/usb-interface.html

1 个赞